# MVME5100 Single Board Computer

# Programmer's Reference Guide

V5100A/PG3

July 2003 Edition

## © Copyright 2003 Motorola, Inc.

## All rights reserved.

### Printed in the United States of America.

Motorola and the Motorola logo are registered trademarks and AltiVec is a trademark of Motorola, Inc.

PowerPC and the PowerPC logo are registered trademarks; and PowerPC 750 is a trademark of International Business Machines Corporation and are used by Motorola, Inc. under license from International Business Machines Corporation.

All other products mentioned in this document are trademarks or registered trademarks of their respective holders.

# **Safety Summary**

The following general safety precautions must be observed during all phases of operation, service, and repair of this equipment. Failure to comply with these precautions or with specific warnings elsewhere in this manual could result in personal injury or damage to the equipment.

The safety precautions listed below represent warnings of certain dangers of which Motorola is aware. You, as the user of the product, should follow these warnings and all other safety precautions necessary for the safe operation of the equipment in your operating environment.

#### Ground the Instrument.

To minimize shock hazard, the equipment chassis and enclosure must be connected to an electrical ground. If the equipment is supplied with a three-conductor AC power cable, the power cable must be plugged into an approved three-contact electrical outlet, with the grounding wire (green/yellow) reliably connected to an electrical ground (safety ground) at the power outlet. The power jack and mating plug of the power cable meet International Electrotechnical Commission (IEC) safety standards and local electrical regulatory codes.

### Do Not Operate in an Explosive Atmosphere.

Do not operate the equipment in any explosive atmosphere such as in the presence of flammable gases or fumes. Operation of any electrical equipment in such an environment could result in an explosion and cause injury or damage.

### Keep Away From Live Circuits Inside the Equipment.

Operating personnel must not remove equipment covers. Only Factory Authorized Service Personnel or other qualified service personnel may remove equipment covers for internal subassembly or component replacement or any internal adjustment. Service personnel should not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, such personnel should always disconnect power and discharge circuits before touching components.

### Use Caution When Exposing or Handling a CRT.

Breakage of a Cathode-Ray Tube (CRT) causes a high-velocity scattering of glass fragments (implosion). To prevent CRT implosion, do not handle the CRT and avoid rough handling or jarring of the equipment. Handling of a CRT should be done only by qualified service personnel using approved safety mask and gloves.

### Do Not Substitute Parts or Modify Equipment.

Do not install substitute parts or perform any unauthorized modification of the equipment. Contact your local Motorola representative for service and repair to ensure that all safety features are maintained.

### **Observe Warnings in Manual.**

Warnings, such as the example below, precede potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed. You should also employ all other safety precautions which you deem necessary for the operation of the equipment in your operating environment.

To prevent serious injury or death from dangerous voltages, use extreme caution when handling, testing, and adjusting this equipment and its components.

# **Flammability**

All Motorola PWBs (printed wiring boards) are manufactured with a flammability rating of 94V-0 by UL-recognized manufacturers.

#### **EMI Caution**

This equipment generates, uses and can radiate electromagnetic energy. It may cause or be susceptible to electromagnetic interference (EMI) if not installed and used with adequate EMI protection.

# **Lithium Battery Caution**

This product contains a lithium battery to power the clock and calendar circuitry.

Danger of explosion if battery is replaced incorrectly. Replace battery only with the same or equivalent type recommended by the equipment manufacturer. Dispose of used batteries according to the manufacturer's instructions.

Il y a danger d'explosion s'il y a remplacement incorrect de la batterie. Remplacer uniquement avec une batterie du même type ou d'un type équivalent recommandé par le constructeur. Mettre au rebut les batteries usagées conformément aux instructions du fabricant.

Explosionsgefahr bei unsachgemäßem Austausch der Batterie. Ersatz nur durch denselben oder einen vom Hersteller empfohlenen Typ. Entsorgung gebrauchter Batterien nach Angaben des Herstellers.

# **CE Notice (European Community)**

Motorola Computer Group products with the CE marking comply with the EMC Directive (89/336/EEC). Compliance with this directive implies conformity to the following European Norms:

EN55022 "Limits and Methods of Measurement of Radio Interference Characteristics of Information Technology Equipment"; this product tested to Equipment Class B

EN55024 "Information technology equipment—Immunity characteristics—Limits and methods of measurement"

Board products are tested in a representative system to show compliance with the above mentioned requirements. A proper installation in a CE-marked system will maintain the required EMC performance.

In accordance with European Community directives, a "Declaration of Conformity" has been made and is available on request. Please contact your sales representative.

#### **Notice**

While reasonable efforts have been made to assure the accuracy of this document, Motorola, Inc. assumes no liability resulting from any omissions in this document, or from the use of the information obtained therein. Motorola reserves the right to revise this document and to make changes from time to time in the content hereof without obligation of Motorola to notify any person of such revision or changes.

Electronic versions of this material may be read online, downloaded for personal use, or referenced in another document as a URL to the Motorola Computer Group website. The text itself may not be published commercially in print or electronic form, edited, translated, or otherwise altered without the permission of Motorola, Inc.

It is possible that this publication may contain reference to or information about Motorola products (machines and programs), programming, or services that are not available in your country. Such references or information must not be construed to mean that Motorola intends to announce such Motorola products, programming, or services in your country.

# **Limited and Restricted Rights Legend**

If the documentation contained herein is supplied, directly or indirectly, to the U.S. Government, the following notice shall apply unless otherwise agreed to in writing by Motorola, Inc.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (b)(3) of the Rights in Technical Data clause at DFARS 252.227-7013 (Nov. 1995) and of the Rights in Noncommercial Computer Software and Documentation clause at DFARS 252.227-7014 (Jun. 1995).

Motorola, Inc. Computer Group 2900 South Diablo Way Tempe, Arizona 85282

# **Contents**

| <b>About This Manual</b> |                                                 |

|--------------------------|-------------------------------------------------|

| Summary of Changes       | xviii                                           |

| Overview of Contents     | xviii                                           |

| Comments and Sugges      | tionsxix                                        |

|                          | his Manual xix                                  |

|                          | XX                                              |

|                          |                                                 |

| CHAPTER 1 Product I      | Data and Memory Maps                            |

| Introduction             | 1-1                                             |

| Memory maps              | 1-4                                             |

| Processor Memory         | / Map1-4                                        |

| Default Proce            | ssor Memory Map1-4                              |

| Processor Me             | mory Map1-5                                     |

| PCI Memory               | Map1-7                                          |

| VME Memor                | y Map1-7                                        |

| PCI Local Bus Me         | emory Map1-8                                    |

| VMEbus Memory            | Map1-8                                          |

| System Bus               | 1-8                                             |

| Processors               | 1-9                                             |

| Processor Type Ide       | entification1-9                                 |

| Processor PLL Co         | nfiguration1-9                                  |

| L2 Cache                 | 1-9                                             |

| L2 Cache SRAM            | Size1-10                                        |

| Cache Speed              | 1-10                                            |

| FLASH Memory.            | 1-10                                            |

| ECC Memory               | 1-11                                            |

| P2 I/O Modes             | 1-11                                            |

| Serial Presence De       | etect (SPD) Definitions1-12                     |

| Hawk ASIC                | 1-12                                            |

| Hawk I2C interfac        | te and configuration information1-13            |

| Vital Product Data       | (VPD) and Serial Presence Detect (SPD) Data1-14 |

| PCI Local Bus            | 1-15                                            |

| PCI Arbitration A        | ssignments for Hawk ASIC1-15                    |

|                          | roller1-16                                      |

| PMC/PCI Expansi          | on Slots 1-17                                   |

| DOLG C G                                                                                                                                                                                                                                                                       | 1-17                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| PCI Configuration Space                                                                                                                                                                                                                                                        | 1-19                             |

| Hawk External Register Bus Address Assignments                                                                                                                                                                                                                                 | 1-21                             |

| MVME5100 Hawk External Register Bus Summary                                                                                                                                                                                                                                    | 1-21                             |

| Dual TL16C550 UARTs                                                                                                                                                                                                                                                            | 1-23                             |

| Status Register                                                                                                                                                                                                                                                                | 1-24                             |

| MODFAIL Bit Register                                                                                                                                                                                                                                                           | 1-25                             |

| MODRST Bit Register                                                                                                                                                                                                                                                            | 1-26                             |

| TBEN Bit Register                                                                                                                                                                                                                                                              |                                  |

| NVRAM/RTC & Watchdog Timer                                                                                                                                                                                                                                                     |                                  |

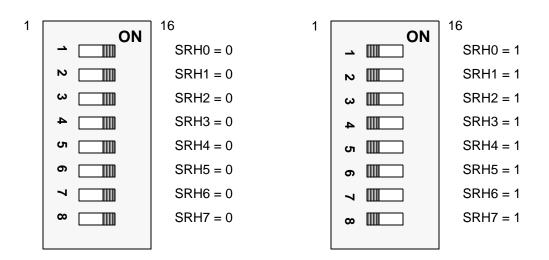

| Software Readable Header/Switch Register (S1)                                                                                                                                                                                                                                  | 1-29                             |

| Geographical Address Register (VME board)                                                                                                                                                                                                                                      |                                  |

| Extended Features Register 1                                                                                                                                                                                                                                                   | 1-31                             |

| Board Last Reset Register                                                                                                                                                                                                                                                      | 1-32                             |

| Extended Features Register 2                                                                                                                                                                                                                                                   | 1-33                             |

| IPMC7xx ISA Bus Resources                                                                                                                                                                                                                                                      | 1-34                             |

| W83C554 PIB Registers                                                                                                                                                                                                                                                          | 1-34                             |

| PC87308VUL Super I/O (ISASIO) Strapping                                                                                                                                                                                                                                        |                                  |

| Z85230 ESCC and Z8536 CIO Registers and Port Pins                                                                                                                                                                                                                              | 1-35                             |

| Z8536/Z85230 Registers                                                                                                                                                                                                                                                         | 1-35                             |

| Z8536 CIO Port Pins                                                                                                                                                                                                                                                            | 1-36                             |

| 20330 CTO 1 Off 1 III5                                                                                                                                                                                                                                                         | 1-30                             |

| ISA DMA Channels                                                                                                                                                                                                                                                               |                                  |

|                                                                                                                                                                                                                                                                                | 1-39                             |

| ISA DMA Channels                                                                                                                                                                                                                                                               | upt Controller                   |

| ISA DMA Channels  CHAPTER 2 Hawk PCI Host Bridge & Multi-Processor Interr  Introduction                                                                                                                                                                                        | 1-39  upt Controller2-1          |

| ISA DMA Channels  CHAPTER 2 Hawk PCI Host Bridge & Multi-Processor Interr                                                                                                                                                                                                      | upt Controller2-1                |

| ISA DMA Channels  CHAPTER 2 Hawk PCI Host Bridge & Multi-Processor Interr  Introduction  Overview  Features                                                                                                                                                                    | 1-39  upt Controller2-12-12-1    |

| ISA DMA Channels  CHAPTER 2 Hawk PCI Host Bridge & Multi-Processor Interr  Introduction  Overview  Features  Block Diagram                                                                                                                                                     | 1-39  upt Controller2-12-12-12-3 |

| ISA DMA Channels  CHAPTER 2 Hawk PCI Host Bridge & Multi-Processor Interr  Introduction  Overview  Features  Block Diagram  Functional Description                                                                                                                             |                                  |

| ISA DMA Channels  CHAPTER 2 Hawk PCI Host Bridge & Multi-Processor Interr  Introduction  Overview  Features  Block Diagram  Functional Description  Architectural Overview                                                                                                     |                                  |

| ISA DMA Channels  CHAPTER 2 Hawk PCI Host Bridge & Multi-Processor Interr  Introduction Overview Features Block Diagram Functional Description Architectural Overview PPC Bus Interface                                                                                        |                                  |

| ISA DMA Channels  CHAPTER 2 Hawk PCI Host Bridge & Multi-Processor Interr  Introduction  Overview  Features  Block Diagram  Functional Description  Architectural Overview                                                                                                     |                                  |

| ISA DMA Channels  CHAPTER 2 Hawk PCI Host Bridge & Multi-Processor Interr  Introduction Overview Features Block Diagram Functional Description Architectural Overview PPC Bus Interface PPC Address Mapping                                                                    |                                  |

| ISA DMA Channels  CHAPTER 2 Hawk PCI Host Bridge & Multi-Processor Interr  Introduction Overview Features Block Diagram Functional Description Architectural Overview PPC Bus Interface PPC Address Mapping PPC Slave                                                          |                                  |

| ISA DMA Channels  CHAPTER 2 Hawk PCI Host Bridge & Multi-Processor Interr  Introduction Overview Features Block Diagram Functional Description Architectural Overview PPC Bus Interface PPC Address Mapping PPC Slave PPC FIFO                                                 |                                  |

| ISA DMA Channels  CHAPTER 2 Hawk PCI Host Bridge & Multi-Processor Interr  Introduction Overview Features Block Diagram Functional Description Architectural Overview PPC Bus Interface PPC Address Mapping PPC Slave PPC FIFO PPC Master                                      |                                  |

| ISA DMA Channels  CHAPTER 2 Hawk PCI Host Bridge & Multi-Processor Interr  Introduction Overview Features Block Diagram Functional Description Architectural Overview PPC Bus Interface PPC Address Mapping PPC Slave PPC FIFO PPC Master PPC Arbiter                          |                                  |

| ISA DMA Channels  CHAPTER 2 Hawk PCI Host Bridge & Multi-Processor Interr  Introduction Overview Features Block Diagram Functional Description Architectural Overview PPC Bus Interface PPC Address Mapping PPC Slave PPC FIFO PPC Master PPC Arbiter PPC Parity               |                                  |

| ISA DMA Channels  CHAPTER 2 Hawk PCI Host Bridge & Multi-Processor Interr  Introduction Overview Features Block Diagram Functional Description Architectural Overview PPC Bus Interface PPC Address Mapping PPC Slave PPC FIFO PPC Master PPC Arbiter PPC Parity PPC Bus Timer |                                  |

|    | PCI Slave                                        | .2-22 |

|----|--------------------------------------------------|-------|

|    | PCI FIFO                                         | .2-26 |

|    | PCI Master                                       | .2-26 |

|    | Generating PCI Cycles                            | .2-29 |

|    | PCI Arbiter                                      | .2-34 |

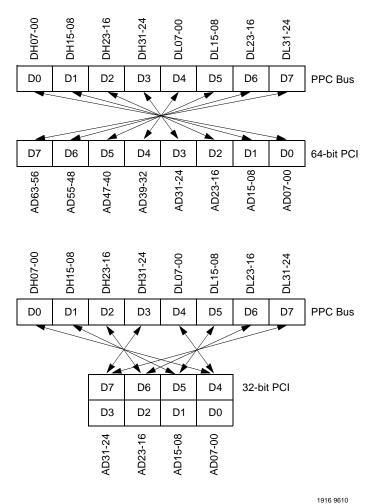

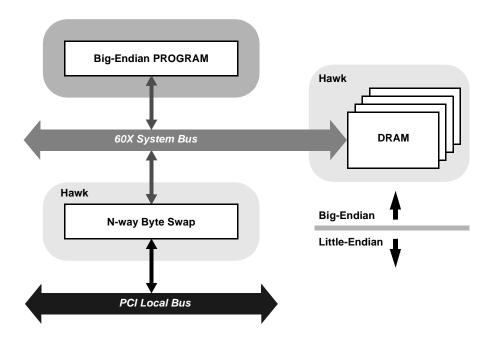

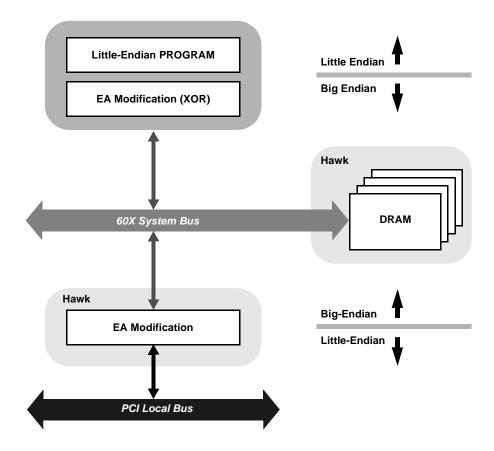

|    | Endian Conversion                                | .2-38 |

|    | When PPC Devices are Big-Endian                  | .2-38 |

|    | When PPC Devices are Little Endian               | .2-39 |

|    | PHB Registers                                    | .2-40 |

|    | Error Handling                                   | .2-41 |

|    | Watchdog Timers                                  |       |

|    | PCI/PPC Contention Handling                      | .2-45 |

|    | Transaction Ordering                             | .2-48 |

|    | PHB Hardware Configuration                       |       |

| Mu | lti-Processor Interrupt Controller (MPIC)        | .2-51 |

|    | MPIC Features:                                   | .2-51 |

|    | Architecture                                     | .2-51 |

|    | External Interrupt Interface                     | .2-52 |

|    | CSR's Readability                                | .2-53 |

|    | Interrupt Source Priority                        | .2-53 |

|    | Processor's Current Task Priority                | .2-54 |

|    | Nesting of Interrupt Events                      | .2-54 |

|    | Spurious Vector Generation                       | .2-54 |

|    | Interprocessor Interrupts (IPI)                  | .2-55 |

|    | 8259 Compatibility                               | .2-55 |

|    | Hawk Internal Errror Interrupt                   | .2-55 |

|    | Timers                                           | .2-56 |

|    | Interrupt Delivery Modes                         | .2-56 |

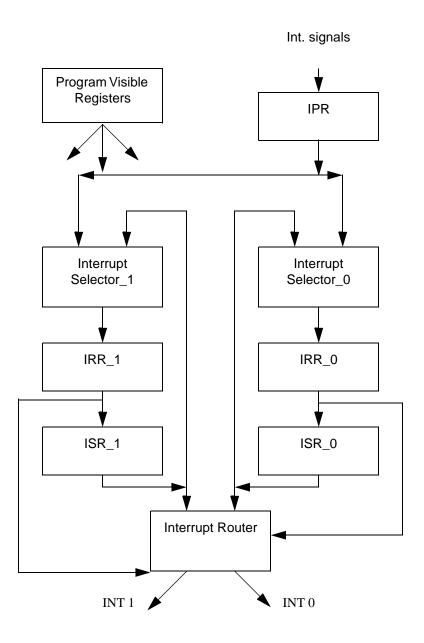

|    | Block Diagram Description                        |       |

|    | Program Visible Registers                        |       |

|    | Interrupt Pending Register (IPR)                 |       |

|    | Interrupt Selector (IS)                          |       |

|    | Interrupt Request Register (IRR)                 |       |

|    | In-Service Register (ISR)                        |       |

|    | Interrupt Router                                 | .2-60 |

|    | Programming Notes                                |       |

|    | External Interrupt Service                       |       |

|    | Reset State                                      |       |

|    | Operation                                        |       |

|    | Interprocessor Interrupts                        |       |

|    | Dynamically Changing I/O Interrupt Configuration |       |

|    | EOI Register                                     | .2-65 |

| Interrupt Acknowledge Register2-65                       |  |

|----------------------------------------------------------|--|

| 8259 Mode2-65                                            |  |

| Current Task Priority Level2-65                          |  |

| Architectural Notes2-66                                  |  |

| Effects of Interrupt Serialization2-66                   |  |

| sters                                                    |  |

| PPC Registers2-68                                        |  |

| Vendor ID/Device ID Registers2-70                        |  |

| Revision ID Register2-70                                 |  |

| General Control-Status/Feature Registers2-71             |  |

| PPC Arbiter/PCI Arbiter Control Registers2-73            |  |

| Hardware Control-Status/Prescaler Adjust Register2-77    |  |

| PPC Error Test/Error Enable Register2-79                 |  |

| PPC Error Status Register                                |  |

| PPC Error Address Register2-84                           |  |

| PPC Error Attribute Register2-85                         |  |

| PCI Interrupt Acknowledge Register2-87                   |  |

| PPC Slave Address (0,1 and 2) Registers2-88              |  |

| PPC Slave Offset/Attribute (0, 1 and 2) Registers        |  |

| PPC Slave Address (3) Register2-90                       |  |

| PPC Slave Offset/Attribute (3) Registers                 |  |

| WDTxCNTL Registers2-92                                   |  |

| WDTxSTAT Registers2-96                                   |  |

| General Purpose Registers2-96                            |  |

| PCI Registers2-97                                        |  |

| Vendor ID/ Device ID Registers                           |  |

| PCI Command/ Status Registers                            |  |

| Revision ID/ Class Code Registers2-101                   |  |

| Header Type Register2-101                                |  |

| MPIC I/O Base Address Register2-102                      |  |

| MPIC Memory Base Address Register2-102                   |  |

| PCI Slave Address (0,1,2, and 3) Registers2-103          |  |

| PCI Slave Attribute/ Offset (0,1,2 and 3) Registers2-104 |  |

| CONFIG_ADDRESS Register2-106                             |  |

| CONFIG_DATA Register2-109                                |  |

| MPIC Registers2-110                                      |  |

| MPIC Registers2-110                                      |  |

| Feature Reporting Register2-113                          |  |

| Global Configuration Register2-114                       |  |

| Vendor Identification Register                           |  |

| Processor Init Register2-116                             |  |

| IPI Vector/Priority Registers                            |  |

| Spurious Vector Register                               | 2-118 |

|--------------------------------------------------------|-------|

| Timer Frequency Register                               | 2-118 |

| Timer Current Count Registers                          | 2-119 |

| Timer Basecount Registers                              | 2-120 |

| Timer Vector/Priority Registers                        | 2-121 |

| Timer Destination Registers                            | 2-122 |

| External Source Vector/Priority Registers              | 2-122 |

| External Source Destination Registers                  |       |

| Hawk Internal Error Interrupt Vector/Priority Register |       |

| Hawk Internal Error Interrupt Destination Register     |       |

| Interprocessor Interrupt Dispatch Registers            |       |

| Current Task Priority Registers                        |       |

| Interrupt Acknowledge Registers                        |       |

| End-of-Interrupt Registers                             | 2-128 |

|                                                        |       |

| CHAPTER 3 System Memory Controller (SMC)               |       |

| Introduction                                           | 3-1   |

| Overview                                               |       |

| Bit Ordering Convention                                |       |

| Features                                               |       |

| Block Diagrams                                         |       |

| Functional Description                                 |       |

| SDRAM Accesses                                         |       |

| Four-beat Reads/Writes                                 |       |

| Single-beat Reads/Writes                               |       |

| Address Pipelining                                     |       |

| Page Holding                                           |       |

| SDRAM Speeds                                           |       |

| SDRAM Organization                                     |       |

| PPC60x Bus Interface                                   | 3-9   |

| Responding to Address Transfers                        | 3-9   |

| Completing Data Transfers                              | 3-9   |

| PPC60x Data Parity                                     | 3-10  |

| PPC60x Address Parity                                  | 3-10  |

| Cache Coherency                                        | 3-11  |

| Cache Coherency Restrictions                           |       |

| L2 Cache Support                                       |       |

| SDRAM ECC                                              |       |

| Cycle Types                                            |       |

| Error Reporting                                        | 3-12  |

| Error Logging                                      | . 3-13 |

|----------------------------------------------------|--------|

| ROM/Flash Interface                                | .3-14  |

| ROM/Flash Speeds                                   | .3-19  |

| I2C Interface                                      | . 3-22 |

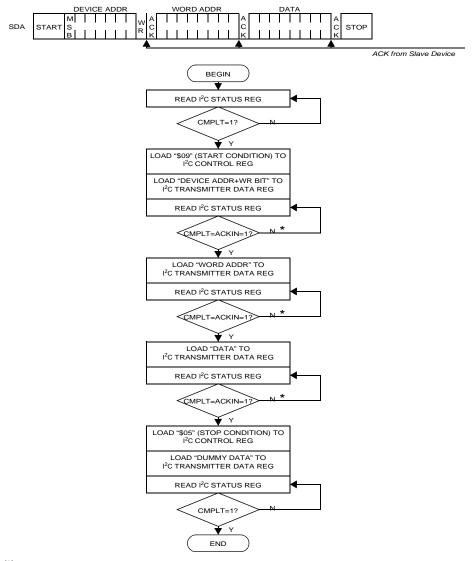

| I2C Byte Write                                     | . 3-23 |

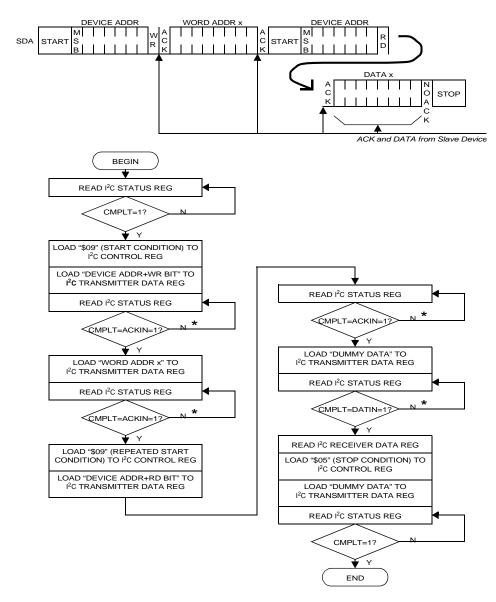

| I2C Random Read                                    |        |

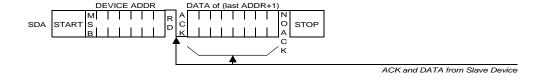

| I2C Current Address Read                           | . 3-27 |

| I2C Page Write                                     | .3-29  |

| I2C Sequential Read                                | .3-31  |

| Refresh/Scrub                                      | .3-34  |

| CSR Accesses.                                      | . 3-34 |

| External Register Set                              | . 3-34 |

| Chip Configuration                                 | .3-35  |

| Programming Model                                  | . 3-35 |

| CSR Architecture                                   | . 3-35 |

| Register Summary                                   | . 3-36 |

| Detailed Register Bit Descriptions                 | .3-38  |

| Vendor/Device Register                             | .3-39  |

| Revision ID/General Control Register               | .3-39  |

| SDRAM Enable and Size Register (Blocks A, B, C, D) | .3-41  |

| SDRAM Base Address Register (Blocks A/B/C/D)       | .3-43  |

| CLK Frequency Register                             | . 3-44 |

| ECC Control Register                               | . 3-46 |

| Error Logger Register                              | . 3-50 |

| Error_Address Register                             | . 3-52 |

| Scrub/Refresh Register                             | . 3-52 |

| Scrub Address Register                             | .3-53  |

| ROM A Base/Size Register                           | . 3-54 |

| ROM B Base/Size Register                           | . 3-57 |

| ROM Speed Attributes Registers                     |        |

| Data Parity Error Log Register                     |        |

| Data Parity Error Address Register                 |        |

| Data Parity Error Upper Data Register              |        |

| Data Parity Error Lower Data Register              |        |

| I2C Clock Prescaler Register                       | . 3-64 |

| I2C Control Register                               | . 3-64 |

| I2C Status Register                                |        |

| I2C Transmitter Data Register                      |        |

| I2C Receiver Data Register                         |        |

| SDRAM Enable and Size Register (Blocks E,F,G,H)    |        |

| SDRAM Base Address Register (Blocks E/F/G/H)       |        |

| SDRAM Speed Attributes Register                    | . 3-69 |

| Address Parity Error Log Register                                   | 3-71 |

|---------------------------------------------------------------------|------|

| Address Parity Error Address Register                               | 3-72 |

| 32-Bit Counter                                                      | 3-73 |

| External Register Set                                               | 3-73 |

| tben Register                                                       | 3-74 |

| Software Considerations                                             | 3-75 |

| Programming ROM/Flash Devices                                       | 3-75 |

| Writing to the Control Registers                                    | 3-75 |

| Initializing SDRAM Related Control Registers                        |      |

| SDRAM Speed Attributes                                              | 3-76 |

| SDRAM Size                                                          | 3-77 |

| I2C EEPROMs                                                         | 3-77 |

| SDRAM Base Address and Enable                                       | 3-77 |

| SDRAM Control Registers Initialization Example                      | 3-78 |

| Optional Method for Sizing SDRAM                                    | 3-84 |

| ECC Codes                                                           | 3-87 |

| Introduction PCI Arbitration                                        |      |

| PCI Arbitration.                                                    |      |

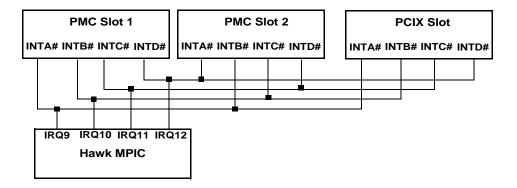

| Hawk MPIC External Interrupts                                       |      |

| 8259 Interrupts                                                     |      |

| Exceptions                                                          |      |

| Sources of Reset                                                    |      |

| Soft Reset                                                          |      |

| CPU Reset                                                           |      |

| Error Notification and Handling                                     |      |

| Endian Issues                                                       |      |

| Processor/Memory Domain                                             |      |

| MPIC's Involvement                                                  |      |

| DCT Domain                                                          |      |

| PCI Domain                                                          |      |

| APPENDIX A Related Documentation                                    |      |

| APPENDIX A Related Documentation                                    | 4-9  |

|                                                                     | 4-9  |

| APPENDIX A Related Documentation  Motorola Computer Group Documents | A-9  |

## APPENDIX B MVME5100 VPD Reference Information

| Vital Product Data (VPD) Introduction                | B-1         |

|------------------------------------------------------|-------------|

| How to Read the VPD Information                      | B-1         |

| How to Modify the VPD Information                    | B-2         |

| What Happens if the VPD Information is Corrupted?    | B-3         |

| How to Fix Corrupted VPD Information                 | B-3         |

| What if Your Board Has the Wrong VPD?                | B-3         |

| How to Fix Wrong VPD Problems                        | B-3         |

| VPD Definitions - Packet Types                       | B-4         |

| VPD Definitions - Product Configuration Options Data | B-7         |

| VPD Definitions - FLASH Memory Configuration Data    | <b>B</b> -9 |

| VPD Definitions - L2 Cache Configuration Data        | B-10        |

| VPD Definitions - VPD Revision Data                  | B-12        |

| Configuration Checksum Calculation Code              | B-14        |

| Serial Presence Detect (SPD) Checksum Calculation    | B-15        |

|                                                      |             |

| APPENDIX C VMEbus Mapping Example                    |             |

| Introduction                                         | C-1         |

# **List of Figures**

| Figure 1-1. MVME5100 Block Diagram                                      | 1-3  |

|-------------------------------------------------------------------------|------|

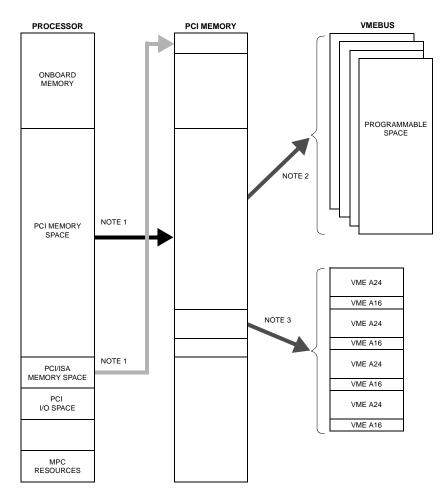

| Figure 1-2. VMEbus Master Mapping                                       | 1-18 |

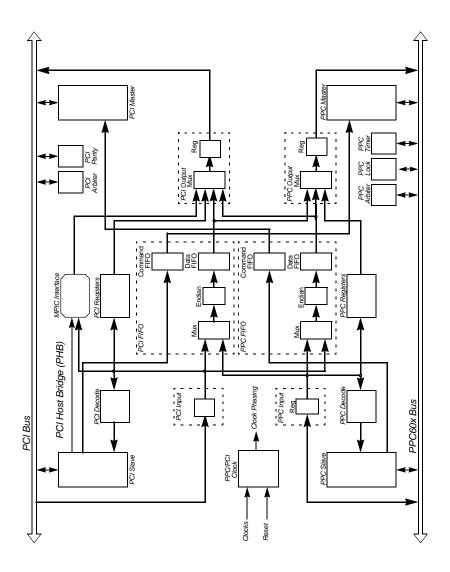

| Figure 2-1. Hawk PCI Host Bridge Block Diagram                          | 2-3  |

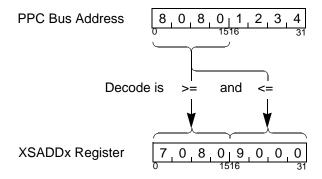

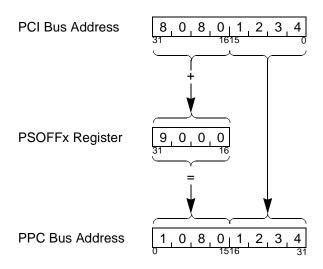

| Figure 2-2. PPC to PCI Address Decoding                                 | 2-6  |

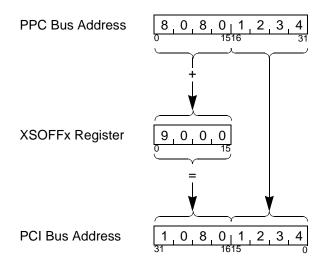

| Figure 2-3. PPC to PCI Address Translation                              | 2-7  |

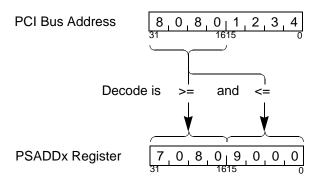

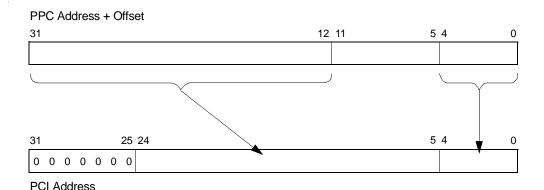

| Figure 2-4. PCI to PPC Address Decoding                                 | 2-20 |

| Figure 2-5. PCI to PPC Address Translation                              | 2-21 |

| Figure 2-6. PCI Spread I/O Address Translation                          | 2-31 |

| Figure 2-7. Big-to-Little-Endian Data Swap                              | 2-39 |

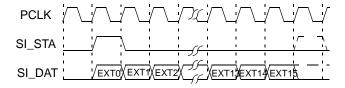

| Figure 2-8. Serial Mode Interrupt Scan                                  | 2-52 |

| Figure 2-9. MPIC Block Diagram                                          | 2-58 |

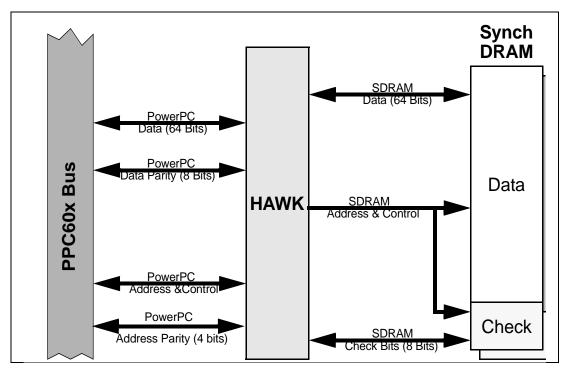

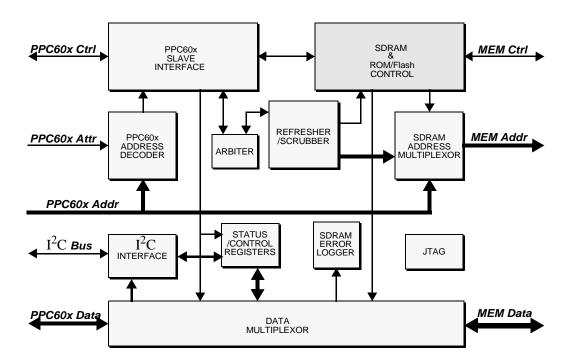

| Figure 3-1. Hawk Used with Synchronous DRAM in a System                 | 3-2  |

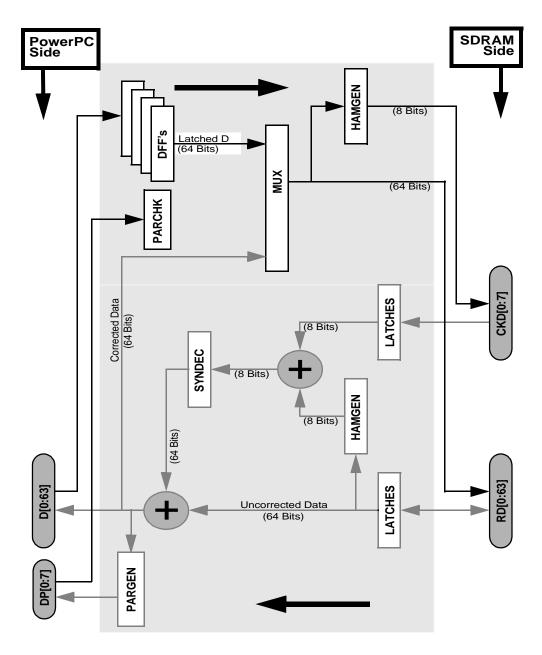

| Figure 3-2. Hawk's System Memory Controller Internal Data Paths         | 3-3  |

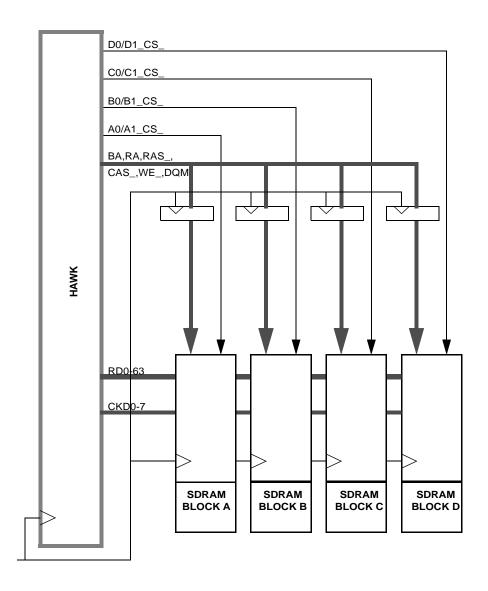

| Figure 3-3. Overall SDRAM Connections (4 Blocks using Register Buffers) | 3-4  |

| Figure 3-4. Hawk's System Memory Controller Block Diagram               | 3-5  |

| Figure 3-5. Programming Sequence for I2C Byte Write                     | 3-24 |

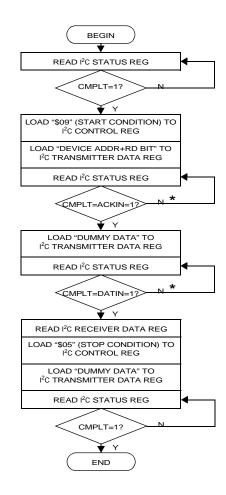

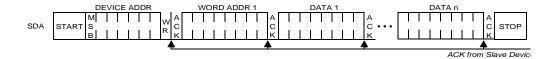

| Figure 3-6. Programming Sequence for I2C Random Read                    | 3-26 |

| Figure 3-7. Programming Sequence for I2C Current Address Read           | 3-28 |

| Figure 3-8. Programming Sequence for I2C Page Write                     | 3-30 |

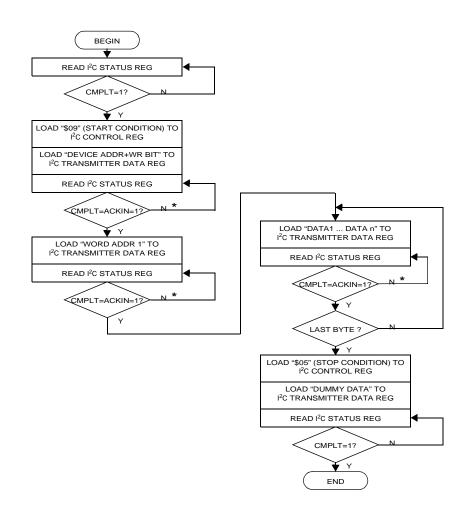

| Figure 3-9. Programming Sequence for I2C Sequential Read                | 3-33 |

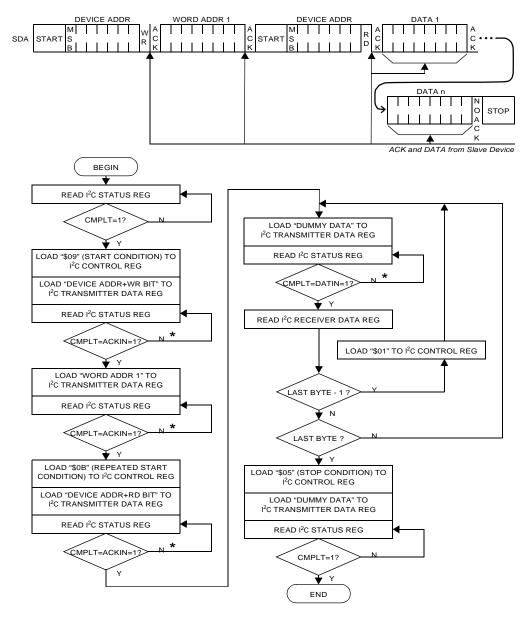

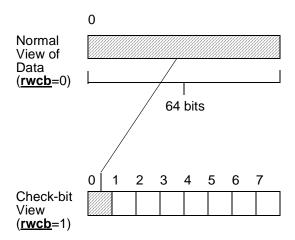

| Figure 3-10. Read/Write Check-bit Data Paths                            | 3-47 |

| Figure 4-1. Big-Endian Mode                                             | 4-7  |

| Figure 4-2. Little-Endian Mode                                          | 4-8  |

# **List of Tables**

| Table 1-1. MVME Key Features                                    | 1-1  |

|-----------------------------------------------------------------|------|

| Table 1-2. Default Processor Memory Map                         | 1-4  |

| Table 1-3. Suggested CHRP Memory Map                            | 1-6  |

| Table 1-4. Hawk PPC Register Values for Suggested Memory Map    | 1-7  |

| Table 1-5. I2C Device Addressing                                | 1-14 |

| Table 1-6. PCI Arbitration Assignments                          | 1-15 |

| Table 1-7. IDSEL Mapping for PCI Devices                        | 1-19 |

| Table 1-8. On-Board PCI Device Identification                   | 1-20 |

| Table 1-9. Hawk External Register Bus Summary                   | 1-21 |

| Table 1-10. 16550 Access Registers                              | 1-23 |

| Table 1-11. MVME5100 Status Register                            | 1-24 |

| Table 1-12. MODFAIL Bit Register                                | 1-25 |

| Table 1-13. MODRST Bit Register                                 | 1-26 |

| Table 1-14. TBEN Bit Register                                   | 1-27 |

| Table 1-15. M48T37V Access Registers                            | 1-28 |

| Table 1-16. Extended Features Register 1                        |      |

| Table 1-17. Extended Features Register 2                        | 1-33 |

| Table 1-18. Strap Pins Configuration for the PC87308VUL         |      |

| Table 1-19. Z8536/Z85230 Access Registers                       | 1-35 |

| Table 1-20. Z8536 CIO Port Pins Assignment                      |      |

| Table 1-21. Interpretation of MID3-MID0                         | 1-37 |

| Table 1-22. PIB DMA Channel Assignments                         | 1-39 |

| Table 2-1. PPC Slave Response Command Types                     | 2-8  |

| Table 2-2. PPC Master Transaction Profiles and Starting Offsets | 2-11 |

| Table 2-3. PPC Master Write Posting Options                     | 2-12 |

| Table 2-4. PPC Master Read Ahead Options                        | 2-12 |

| Table 2-5. PPC Master Transfer Types                            |      |

| Table 2-6. PPC Arbiter Pin Assignments                          | 2-15 |

| Table 2-7. PCI Slave Response Command Types                     | 2-23 |

| Table 2-8. PCI Master Command Codes                             | 2-27 |

| Table 2-9. PCI Arbiter Pin Description                          | 2-34 |

| Table 2-10. Fixed Mode Priority Level Setting                   | 2-35 |

| Table 2-11. Mixed Mode Priority Level Setting                   | 2-36 |

| Table 2-12. Arbitration Setting                                 | 2-37 |

| Table 2-13. Address Modification for Little Endian Transfers             | 2-40  |

|--------------------------------------------------------------------------|-------|

| Table 2-14. WDTxCNTL Programming                                         | 2-44  |

| Table 2-15. PHB Hardware Configuration                                   | 2-50  |

| Table 2-16. PPC Register Map for PHB                                     | 2-68  |

| Table 2-17. PCI Configuration Register                                   | 2-97  |

| Table 2-18. PCI I/O Register                                             | 2-98  |

| Table 2-19. MPIC Register Map                                            | 2-110 |

| Table 2-20. Cascade Mode Encoding                                        | 2-115 |

| Table 2-21. Tie Mode Encoding                                            | 2-115 |

| Table 3-1. 60x Bus to SDRAM Estimated Access Timing at 100 MHz with PC   | 100   |

| SDRAMs (CAS_latency of 2)                                                | 3-7   |

| Table 3-2. Error Reporting.                                              | 3-12  |

| Table 3-3. PPC60x to ROM/Flash (16 Bit Width)                            |       |

| Address Mapping                                                          | 3-16  |

| Table 3-4. PPC60x to ROM/Flash (64 Bit Width)                            |       |

| Address Mapping                                                          | 3-17  |

| Table 3-5. PPC60x Bus to ROM/Flash Access Timing                         |       |

| (120ns @ 100 MHz)                                                        | 3-19  |

| Table 3-6. PPC60x Bus to ROM/Flash Access Timing                         |       |

| (80ns @ 100 MHz)                                                         | 3-20  |

| Table 3-7. PPC60x Bus to ROM/Flash Access Timing                         |       |

| (50ns @ 100 MHz)                                                         | 3-20  |

| Table 3-8. PPC60x Bus to ROM/Flash Access Timing                         |       |

| (30ns @ 100 MHz)                                                         |       |

| Table 3-9. Register Summary                                              |       |

| Table 3-10. Block_A/B/C/D/E/F/G/H Configurations                         |       |

| Table 3-11. ROM Block A Size Encoding                                    |       |

| Table 3-12. rom_a_rv and rom_b_rv encoding                               |       |

| Table 3-13. Read/Write to ROM/Flash                                      |       |

| Table 3-14. ROM Block B Size Encoding                                    |       |

| Table 3-15. ROM Speed Bit Encodings                                      |       |

| Table 3-16. Trc Encoding                                                 |       |

| Table 3-17. tras Encoding                                                | 3-70  |

| Table 3-18. Deriving tras, trp, trcd and trc Control Bit Values from SPD |       |

| Information                                                              |       |

| Table 3-19. Programming SDRAM SIZ Bits                                   |       |

| Table 3-20. Address Lists for Different Block Size Checks                |       |

| Table 3-21. Syndrome Codes Ordered by Bit in Error                       |       |

| Table 3-22. Single Bit Errors Ordered by Syndrome Code                   | 3-88  |

| Table 4-1. MPIC Interrupt Assignments                    | 4-1 |

|----------------------------------------------------------|-----|

| Table 4-2. PBC ISA Interrupt Assignments                 | 4-3 |

| Table 4-3. Error Notification and Handling               | 4-6 |

| Table A-1. Motorola Computer Group Documents             |     |

| Table A-2. Manufacturers' Documents                      |     |

| Table A-3. Related Specifications                        | A-4 |

| Table B-1. VPD Packet Types                              |     |

| Table B-2. MCG Product Configuration Options Data        |     |

| Table B-3. FLASH Memory Configuration Data               |     |

| Table B-4. L2 Cache Configuration Data                   |     |

| Table B-5. VPD Revision Data                             |     |

| Table C-1. MVME2700/MVME5100 Sample Slave Image Settings |     |

# **About This Manual**

The MVME5100 Single Board Computer Programmer's Guide provides the information you will need to program and configure your MVME5100 Single Board Computer. It provides specific programming information and data applicable to this board.

This guide provides programming information and other data applicable to the MVME5100. As an added convienience, it also provides details of the chip set (Hawk) programming functions. It is important to note that much of the board's programming functionality is associated with the Hawk ASIC. Additional programming information can also be found in the following manuals (refer to Appendix A, *Related Documentation*):

- PPCBug Firmware Package User's Manual

- □ PPCBug Diagnostics Manual

- □ MPC750 RISC Microprocessor User's Manual

- □ MPC7410 RISC Microprocessor User's Manual

- □ Universe II User Manual

The MVME5100 is a high-performance VME single board computer featuring the Motorola Computer Group (MCG) PowerPlus II architecture with a choice of PowerPC® processors—either Motorola's MPC7410 with AltiVec technology for algorithmic intensive computations or the low-power MPC750 and MPC755.

As of the printing date of this manual, the MVME5100 is available in the configurations shown below.

| Part Number                                 | Description                                                                                                                                                                                                                                         |  |  |  |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                             | 450 MHz MPC750 Commercial Models                                                                                                                                                                                                                    |  |  |  |

| MVME5100-016x                               | 6x 450 MHz MPC750, 512MB ECC SDRAM, 17MB Flash and 1MB L2 cache                                                                                                                                                                                     |  |  |  |

|                                             | 400 MHz MPC755 Extended Temperature Models                                                                                                                                                                                                          |  |  |  |

| MVME5106-114x                               | 400 MHz MPC755, 128MB ECC SDRAM, 17MB Flash and 1MB L2 cache                                                                                                                                                                                        |  |  |  |

| MVME5106-115x                               | 400 MHz MPC755, 256MB ECC SDRAM, 17MB Flash and 1MB L2 cache                                                                                                                                                                                        |  |  |  |

| MVME5106-116x                               | 400 MHz MPC755, 512MB ECC SDRAM, 17MB Flash and 1MB L2 cache                                                                                                                                                                                        |  |  |  |

|                                             | 400 and 500 MHz MPC7410 Commercial Models                                                                                                                                                                                                           |  |  |  |

| MVME5110-216x                               | 400 MHz MPC7410, 512MB ECC SDRAM, 17MB Flash and 2MB L2 cache                                                                                                                                                                                       |  |  |  |

| MVME5110-226x                               | 500 MHz MPC7410, 512MB ECC SDRAM, 17MB Flash and 2MB L2 cache                                                                                                                                                                                       |  |  |  |

| 500 MHz MPC7410 Extended Temperature Models |                                                                                                                                                                                                                                                     |  |  |  |

| MVME5107-214x                               | 500 MHz MPC7410, 128MB ECC SDRAM, 17MB Flash and 2MB L2 cache                                                                                                                                                                                       |  |  |  |

| MVME5107-215x                               | 500 MHz MPC7410, 256MB ECC SDRAM, 17MB Flash and 2MB L2 cache                                                                                                                                                                                       |  |  |  |

| MVME5107-216x                               | 500 MHz MPC7410, 512MB ECC SDRAM, 17MB Flash and 2MB L2 cache                                                                                                                                                                                       |  |  |  |

|                                             | MVME712M Compatible I/O                                                                                                                                                                                                                             |  |  |  |

| IPMC712-001                                 | Multifunction rear I/O PMC module; 8-bit SCSI, Ultra Wide SCSI, one parallel port, three async and one sync/async serial port                                                                                                                       |  |  |  |

| MVME712M                                    | Transition module connectors: One DB-25 sync/async serial port, three DB-25 async serial ports, one AUI connector, one D-36 parallel port, and one 50-pin 8-bit SCSI; includes 3-row DIN P2 adapter module and cable.                               |  |  |  |

|                                             | MVME761 Compatible I/O                                                                                                                                                                                                                              |  |  |  |

| IPMC761-001                                 | Multifunction rear I/O PMC module; 8-bit SCSI, one parallel port, two async and two sync/async serial ports                                                                                                                                         |  |  |  |

| MVME761-001                                 | Transition module: Two DB-9 async serial port connectors, two HD-26 sync/async serial port connectors, one HD-36 parallel port connector, and one RJ-45 10/100 Ethernet connector; includes 3-row DIN P2 adapter module and cable (for 8-bit SCSI). |  |  |  |

| Part Number  | Description                                                                                                                                                                                                                                                                                        |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MVME761-011  | Transition module: Two DB-9 async serial port connectors, two HD-26 sync/async serial port connectors, one HD-36 parallel port connector, and one RJ-45 10/100 Ethernet connector; includes 5-row DIN P2 adapter module and cable (for 16-bit SCSI); requires backplane with 5-row DIN connectors. |  |

| SIM232DCE or | EIA-232 DCE or DTE Serial Interface Module                                                                                                                                                                                                                                                         |  |

| DTE          |                                                                                                                                                                                                                                                                                                    |  |

| SIM530DCE or | EIA-530 DCE or DTE Serial Interface Module                                                                                                                                                                                                                                                         |  |

| DTE          |                                                                                                                                                                                                                                                                                                    |  |

| SIMV35DCE or | V.35 DCE or DTE Module                                                                                                                                                                                                                                                                             |  |

| DTE          |                                                                                                                                                                                                                                                                                                    |  |

| SIMX21DCE or | X.21 DCE or DTE Serial Interface Module                                                                                                                                                                                                                                                            |  |

| DTE          |                                                                                                                                                                                                                                                                                                    |  |

|              | Related Products                                                                                                                                                                                                                                                                                   |  |

| PMCSPAN1-002 | PMCSPAN-002 with original VME Scanbe ejector handles                                                                                                                                                                                                                                               |  |

| PMCSPAN1-010 | PMCSAN-010 with original VME Scanbe ejector handles                                                                                                                                                                                                                                                |  |

| RAM500-004   | Stackable (top) 64MB ECC SDRAM mezzanine                                                                                                                                                                                                                                                           |  |

| RAM500-006   | Stackable (top) 256MB ECC SDRAM mezzanine                                                                                                                                                                                                                                                          |  |

| RAM500-016   | Stackable (bottom) 256MB ECC SDRAM mezzanine                                                                                                                                                                                                                                                       |  |

# **Summary of Changes**

The following changes were made for the 2nd revision of this manual.

| Date    | Doc. Rev   | Changes                                                                                                                                                                                                                                                                            |

|---------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 09/2001 | V5100A/PG2 | Memory Maps and additional register information was added to Chapter 1. Corrections were made to Table 4-1 in Chapter 4. Additions were made to Appendix A, Releated Documentation. Appendix B, VPD Information was added. This section titled "About this Manual" was also added. |

| 07/2003 | v5100A/PG3 | Added information at the end of Chapter 1 on IPMC7xx ISA Bus Resources. Corrected incorrect address for DS1621 SROM. Added Appendix C, VMEbus Mapping Example. Added corrections/additions for CLK_FREQUENCY Register in Chapter 3.                                                |

# **Overview of Contents**

The following paragraphs briefly describe the contents of each chapter.

Chapter 1, *Product Data and Memory Maps*, provides a description of the MVME5100, tables of specific memory maps and other control registers.

Chapter 2, *Hawk PCI Host Bridge & Multi-Processor Interrupt Controller*, provides a description of the Hawk's PowerPC to Local Bus Bridge (PHB) and the Multi-Processor Interrupt Controller (MPIC) including a list of features, a block diagram, a functional description and corresponding register tables.

Chapter 3, *System Memory Controller (SMC)*, provides an explanation of the System Memory Controller (SMC) portion of the Hawk ASIC including a features list, block diagrams, functional descriptions, and an explanation and description of all corresponding registers.

Chapter 4, *Hawk Programming Details*, procides a summary of the Hawk programming details that are relevant to every day programming functions, including a listing of the Hawk MPIC External Interrupts, the

8259 Interrupts, and a description of certain exceptions such as sources of reset, error notification and handling, endian issues, and processor/Hawk relationships.

Appendix A, *Related Documentation*, provides a listing of related Motorola manuals, vendor documentation and industry specifications.

Appendix B, *MVME5100 VPD Reference Information*, provides an explanation of the VPD reference information including certain "How to" info, as well as specific VPD Data Definitions.

Appendix C, *VMEbus Mapping Example*, provides an example of a mapping scenario between an MVME5100 and an MVME2700 on a VMEbus backplane.

# **Comments and Suggestions**

Motorola welcomes and appreciates your comments on its documentation. We want to know what you think about our manuals and how we can make them better. Mail comments to:

Motorola Computer Group Reader Comments DW164 2900 S. Diablo Way Tempe, Arizona 85282

You can also submit comments to the following e-mail address: reader-comments@mcg.mot.com

In all your correspondence, please list your name, position, and company. Be sure to include the title and part number of the manual and tell how you used it. Then tell us your feelings about its strengths and weaknesses and any recommendations for improvements.

# **Conventions Used in This Manual**

The following typographical conventions are used in this document:

hold

is used for user input that you type just as it appears; it is also used for commands, options and arguments to commands, and names of programs, directories and files.

#### italic

is used for names of variables to which you assign values. Italic is also used for comments in screen displays and examples, and to introduce new terms.

#### courier

is used for system output (for example, screen displays, reports), examples, and system prompts.

#### <**Enter>**, <**Return>** or <**CR>**

**CR**> represents the carriage return or Enter key.

#### CTRL

represents the Control key. Execute control characters by pressing the Ctrl key and the letter simultaneously, for example, **Ctrl-d**.

# **Terminology**

A character precedes a data or address parameter to specify the numeric format, as follows (if not specified, the format is hexadecimal):

Ox Specifies a hexadecimal number

% Specifies a binary number

& Specifies a decimal number

An asterisk (\*) following a signal name for signals that are *level significant* denotes that the signal is *true* or valid when the signal is low.

An asterisk (\*) following a signal name for signals that are *edge significant* denotes that the actions initiated by that signal occur on high to low transition.

In this manual, *assertion* and *negation* are used to specify forcing a signal to a particular state. In particular, *assertion* and *assert* refer to a signal that is active or true; *negation* and *negate* indicate a signal that is inactive or false. These terms are used independently of the voltage level (high or low) that they represent.

Data and address sizes are defined as follows:

| Byte        | 8 bits, numbered 0 through 7, with bit 0 being the least significant.   |  |

|-------------|-------------------------------------------------------------------------|--|

| Half word   | 16 bits, numbered 0 through 15, with bit 0 being the least significant. |  |

| Word        | 32 bits, numbered 0 through 31, with bit 0 being the least significant. |  |

| Double word | 64 bits, numbered 0 through 63, with bit 0 being the least significant. |  |

# Introduction

The MVME5100 is a state-of-the-art Single Board Computer. It incorporates Motorola's PowerPlus II architecture with a choice of PowerPC processors—either Motorola's MPC7410 with AltiVec<sup>TM</sup> technology for algorithmic intensive computations or the low-power MPC750 or MPC755.

The MVME5100 incorporates a highly optimized PCI interface and memory controller enabling up to 582MB/s memory read bandwidth and 640MB/s burst write bandwidth.

The on-board Hawk ASIC provides the bridge function between the processor's bus and the PCI bus. It provides 32-bit addressing and 64-bit data; however, 64-bit addressing (dual address cycle) is not supported. The ASIC also supports various processor external bus frequencies up to 100 MHz.

**Note** Unless otherwise specified, the designation "MVME5100" refers to all models of the MVME5100-series Single Board Computers.

The following table lists the key features of the MVME5100.

| Feature                                    | Specification                                                                                                                                                            |  |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Microprocessors and<br>Bus Clock Frequency | <ul> <li>MPC7410 @400 or 500 MHz Internal Clock Frequency</li> <li>MPC750 or 755 @450 MHz Internal Clock Frequency</li> <li>Bus Clock Frequency up to 100 MHz</li> </ul> |  |

| L2 Cache (Optional)                        | • 1MB (MPC750) or 2MB (MPC7400) using burst-mod SRAM modules.                                                                                                            |  |

| Memory                                     | <ul> <li>EEPROM, on-board programmable</li> <li>1MB via two 32-pin PLCC/CLCC sockets;</li> <li>16MB Surface Mount</li> </ul>                                             |  |

Table 1-1. MVME Key Features

Table 1-1. MVME Key Features (Continued)

| Feature                | Specification                                                                                                                                                                                                                                                                                                              |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Main Memory<br>(SDRAM) | <ul> <li>PC100 ECC SDRAM with 100 MHz bus</li> <li>32MB to 512MB on board, expandable to<br/>1GB via RAM500 memory mezzanine</li> </ul>                                                                                                                                                                                    |

| NVRAM                  | • 32KB (4KB available for users)                                                                                                                                                                                                                                                                                           |

| Memory Controller      | Hawk System Memory Controller (SMC)                                                                                                                                                                                                                                                                                        |

| PCI Host Bridge        | Hawk PCI Host Bridge (PHB)                                                                                                                                                                                                                                                                                                 |

| Interrupt Controller   | Hawk Multi-Processor Interrupt Controller (MPIC)                                                                                                                                                                                                                                                                           |

| Peripheral Support     | <ul> <li>Dual 16550-Compatible Asynchronous Serial Port's<br/>Routed to the Front Panel RJ-45 Connnector (COM1) and<br/>On-Board Header (COM2)</li> <li>Dual Ethernet Interfaces, one routed to the Front Panel<br/>RJ-45, one routed to the Front Panel RJ-45 or optionally<br/>routed to P2, RJ-45 on MVME761</li> </ul> |

| VMEbus                 | <ul> <li>Tundra Universe Controller, 64-bit PCI</li> <li>Programmable Interrupter &amp; Interrupt Handler</li> <li>Programmable DMA Controller With Link List Support</li> <li>Full System Controller Functions</li> </ul>                                                                                                 |

| PCI/PMC/Expansion      | <ul> <li>Two 32/64-bit PMC Slots with Front-Panel I/O Plus, P2 Rear I/O (MVME2300 Routing)</li> <li>One PCI Expansion Connector (for the PMCSpan)</li> </ul>                                                                                                                                                               |

| Miscellaneous          | <ul> <li>Combined RESET and ABORT Switch</li> <li>Status LEDs</li> </ul>                                                                                                                                                                                                                                                   |

| Form Factor            | • 6U VME                                                                                                                                                                                                                                                                                                                   |

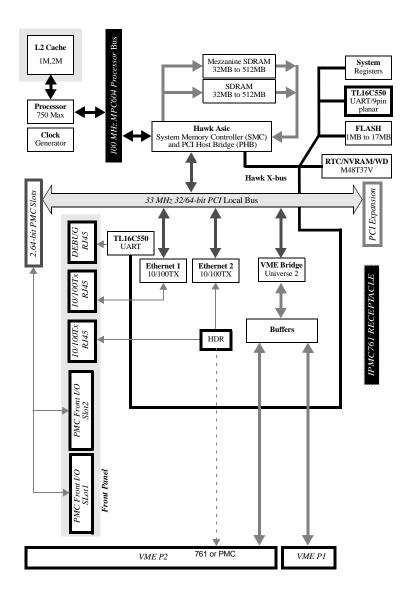

The following block diagram illustrates the architecture of the MVME5100 Single Board Computer.

Figure 1-1. MVME5100 Block Diagram

# **Memory maps**

The following sections describe the memory maps for the MVME5100.

# **Processor Memory Map**

The processor memory map configuration is under the control of the PCI Host Bridge (PHB) and System Memory Controller (SMC) portions of the Hawk ASIC. The Hawk adjusts system mapping to suit a given application via programmable map decoder registers. At system power-up or reset, a default processor memory map takes over.

Following a reset, the memory map presented to the processor is identical to the CHRP memory map described in this document.

The MVME5100 is fully capable of supporting both the PREP and the CHRP processor memory maps with ROM/FLASH size limited to 16MB and RAM size limited to 2GB.

### **Default Processor Memory Map**

The default processor memory map that is valid at power-up or reset remains in effect until reprogrammed for specific applications. Table 1-2 defines the entire default map (\$00000000 to \$FFFFFFF).

Table 1-2. Default Processor Memory Map

| Processor | r Address | Size                                | Definition                         |  |

|-----------|-----------|-------------------------------------|------------------------------------|--|

| Start     | End       | Size                                | Definition                         |  |

| 0000 0000 | 7FFF FFFF | 2GB                                 | Not Mapped                         |  |

| 8000 0000 | 8080 FFFF | 8M+64K Zero-based PCI/ISA I/O Space |                                    |  |

| 8081 0000 | FEF7 FFFF | 2GB-24MB-576KB                      | Not Mapped                         |  |

| FEF8 0000 | FEF8 FFFF | 64KB                                | System Memory Controller Registers |  |

**Processor Address Definition** Size End Start FEF9 0000 FEFE FFFF 384KB Not Mapped FEFF 0000 FEFF FFFF 64KB PCI Host Bridge (PHB) Registers FF00 0000 FFEF FFFF 15MB Not Mapped FFF0 0000 FFFF FFFF 1MB ROM/FLASH Bank A or Bank B (See Note)

**Table 1-2. Default Processor Memory Map (Continued)**

#### Note

The first 1MB of ROM/FLASH Bank A (soldered Flash up to 8MB) appears in this range after a reset if the *rom\_b\_rv* control bit in the SMC's ROM B Base/Size register is cleared. If the *rom\_b\_rv* control bit is set, this address range maps to ROM/FLASH Bank B (socketed 1MB Flash).

For an example of the CHRP memory map refer to the following table. For detailed processor memory maps, including suggested CHRP- and PREP-compatible memory maps, refer to the Hawk related portion of this manual.

## **Processor Memory Map**

The following table describes a suggested CHRP Memory Map from the point of view of the processor. This memory map is an alternative to the PREP memory map. Note: in all recommended CHRP maps, the beginning of PCI Memory Space is determined by the end of DRAM rounded up to the nearest 256MB-boundry as required by CHRP. For example, if memory was 1G on the baseboard and 192MB on a mezzanine, the beginning of PCI memory would be rounded up to address 0x500000000(1G+256M).

Table 1-3. Suggested CHRP Memory Map

| Processor Address |           | Size         | Definition                         | Notes |

|-------------------|-----------|--------------|------------------------------------|-------|

| Start             | End       |              |                                    |       |

| 0000 0000         | top_dram  | dram_size    | System Memory (onboard DRAM)       | 1     |

| top_dram          | F3FF FFFF | 4G-dram_size | PCI Memory Space                   | 1, 5  |

| F400 0000         | F7FF FFFF | 64MB         | FLASH Bank A (optional)            | 1, 2  |

| F800 0000         | FBFF FFFF | 64MB         | FLASH Bank B (optional)            | 1, 2  |

| FC00 0000         | FDFF FFFF | 32MB         | Reserved                           |       |

| FE00 0000         | FE7F FFFF | 8MB          | PCI/ISA I/O Space                  | 1     |

| FE80 0000         | FEF7 FFFF | 7.5MB        | Reserved                           |       |

| FEF8 0000         | FEF8 FFFF | 64KB         | System Memory Controller Registers |       |