# Series IP330 Industrial I/O Pack 16-Bit High Density Analog Input Module

# **USER'S MANUAL**

# **ACROMAG INCORPORATED**

30765 South Wixom Road P.O. BOX 437

Wixom, MI 48393-7037 U.S.A. Tel: (248) 624-1541

Fax: (248) 624-9234

Copyright 1995, Acromag, Inc., Printed in the USA. Data and specifications are subject to change without notice.

8500-485-J03G002

The information contained in this manual is subject to change without notice. Acromag, Inc. makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Further, Acromag, Inc. assumes no responsibility for any errors that may appear in this manual and makes no commitment to update, or keep current, the information contained in this manual. No part of this manual may be copied or reproduced in any form, without the prior written consent of Acromag, Inc.

|     | ile of Contents                                     |

|-----|-----------------------------------------------------|

| 1.0 | GENERAL NFORMATION                                  |

|     | KEY IP330 FEATURES                                  |

|     | INDUSTRIAL I/O PACK INTERFACE FEATURES              |

|     | SIGNAL INTERFACE PRODUCTS                           |

|     | INDUSTRIAL I/O PACK SOFTWARE LIBRARY                |

| 2.0 | PREPARATION FOR USE                                 |

|     | UNPACKING AND INSPECTION                            |

|     | CARD CAGE CONSIDERATIONS                            |

|     | BOARD CONFIGURATION                                 |

|     | Default Hardware Jumper Configuration               |

|     | Analog Input Range Hardware Jumper Configuration    |

|     | Power Supply Hardware Jumper Configuration          |

|     | Software Configuration                              |

|     | CONNECTORS                                          |

|     | IP Field I/O Connector (P2)                         |

|     | Analog Inputs: Noise and Grounding Considerations.  |

|     | External Trigger Input/Output                       |

|     | IP Logic Interface Connector (P1)                   |

| 3.0 | PROGRAMMING INFORMATION                             |

|     | IP IDENTIFICATION PROM                              |

|     | I/O SPACE ADDRESS MAPS                              |

|     | Control Register                                    |

|     | Analog I/P Ranges & Corresponding Digital O/P Codes |

|     | Interrupt Vector Register                           |

|     | Timer Prescaler Register                            |

|     | Conversion Timer Register                           |

|     | Start Channel Value Register                        |

|     | End Channel Value Register                          |

|     | New Data Register                                   |

|     | Missed Data Register                                |

|     | Start Convert Register                              |

|     | Gain Select Registers                               |

|     | Mail Box Buffer                                     |

|     | MODES OF OPERATION                                  |

|     | Uniform Continuous-Mode                             |

|     | Uniform Single-Mode                                 |

|     | Burst Continuous-Mode                               |

|     | Burst Single-Mode                                   |

|     | Convert On External Trigger Only Mode               |

|     | PROGRAMMING CONSIDERATIONS                          |

|     | Use of Calibration Signals                          |

|     | Calibration Programming Example 1                   |

|     | Calibration Programming Example 2                   |

|     | Programming Interrupts                              |

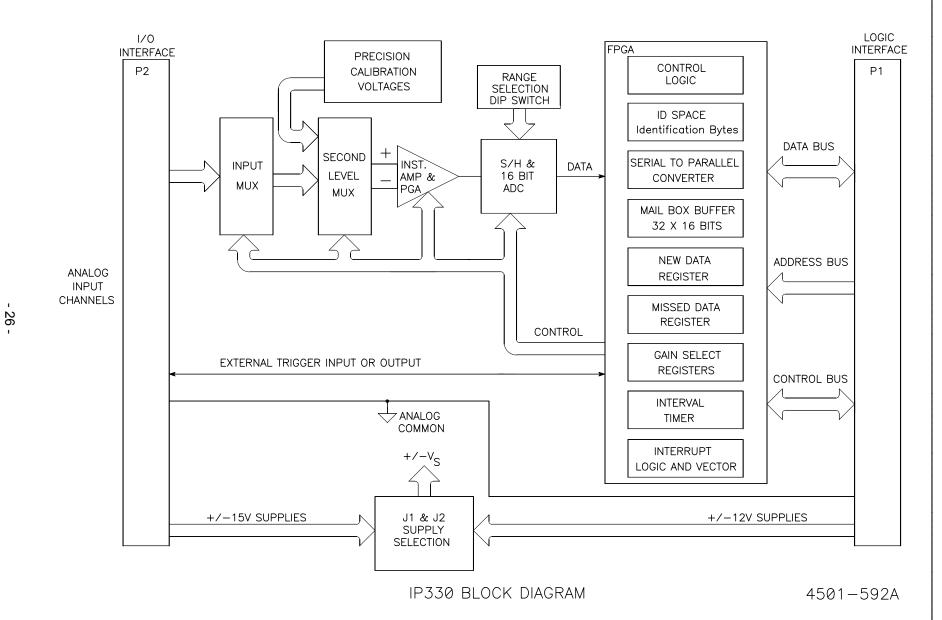

| 4.0 | THEORY OF OPERATION                                 |

| -   | FIELD ANALOG INPUTS                                 |

|     | LOGIC/POWER INTERFACE                               |

|     | IP INTERFACE LOGIC                                  |

|     | IP330 CONTROL LOGIC                                 |

|     | INTERNAL CHANNEL POINTERS                           |

|     | EXTERNAL TRIGGER                                    |

|     | TIMED PERIODIC TRIGGER CIRCUIT                      |

|     | INTERRUPT CONTROL LOGIC                             |

| 5.0 | SERVICE AND REPAIR                                  |

| 5.0 | SERVICE AND REPAIR ASSISTANCE                       |

|     | PRELIMINARY SERVICE PROCEDURE                       |

|     |                                                     |

| 6.0 | SPECIFICATIONS                                                                                           | 20                                 |

|-----|----------------------------------------------------------------------------------------------------------|------------------------------------|

|     | GENERAL SPECIFICATIONS                                                                                   | 20                                 |

|     | ANALOG INPUT                                                                                             | 20                                 |

|     | INDUSTRIAL I/O PACK COMPLIANCE                                                                           | 21                                 |

|     | APPENDIX                                                                                                 | 21                                 |

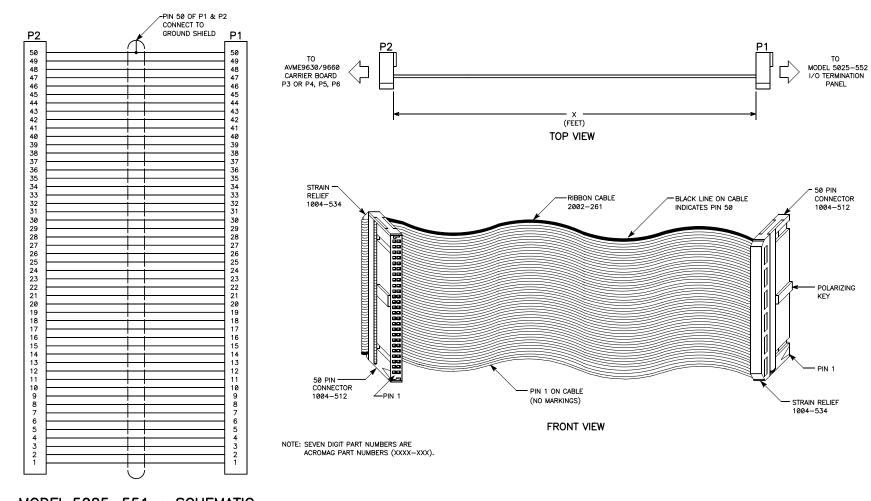

|     | CABLE: MODEL 5025-551                                                                                    | 21                                 |

|     | Recommended APC8600 Shieled Cable                                                                        | 21                                 |

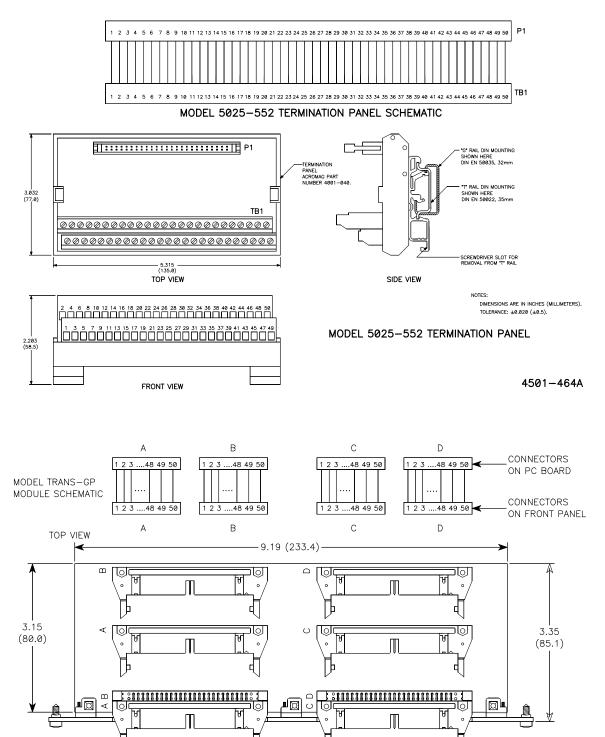

|     | TERMINATION PANEL: MODEL 5025-552                                                                        | 22                                 |

|     | TERMINATION PANEL: MODEL 5029-910                                                                        | 22                                 |

|     | TRANSITION MODULE: MODEL TRANS-GP                                                                        | 22                                 |

|     | TRANSITION MODULE. MODEL TRANS-GP                                                                        | 22                                 |

|     | DRAWINGS                                                                                                 | Page                               |

|     |                                                                                                          |                                    |

|     | DRAWINGS                                                                                                 | Page                               |

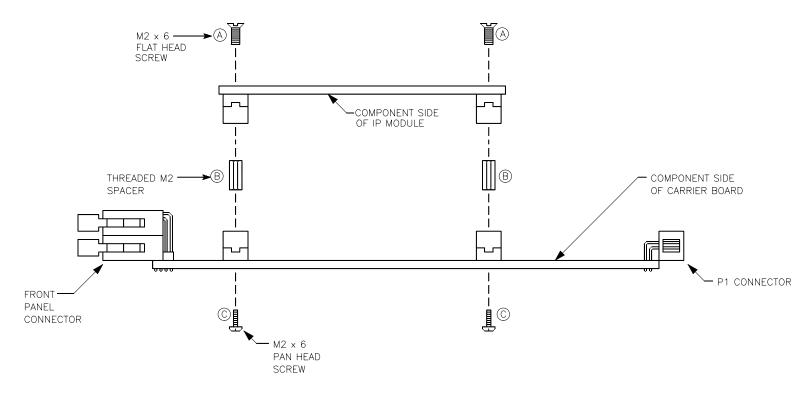

|     | DRAWINGS<br>4501-434 IP MECHANICAL ASSEMBLY                                                              | <b>Page</b> 23                     |

|     | DRAWINGS 4501-434 IP MECHANICAL ASSEMBLY4501-590 IP330 JUMPER LOCATION                                   | Page<br>23<br>24                   |

|     | DRAWINGS 4501-434 IP MECHANICAL ASSEMBLY 4501-590 IP330 JUMPER LOCATION 4501-591 ANALOG INPUT CONNECTION | Page<br>23<br>24<br>25             |

|     | DRAWINGS 4501-434 IP MECHANICAL ASSEMBLY                                                                 | Page<br>23<br>24<br>25<br>26       |

|     | DRAWINGS         4501-434       IP MECHANICAL ASSEMBLY                                                   | Page<br>23<br>24<br>25<br>26<br>27 |

#### **IMPORTANT SAFETY CONSIDERATIONS**

It is very important for the user to consider the possible adverse effects of power, wiring, component, sensor, or software failures in designing any type of control or monitoring system. This is especially important where economic property loss or human life is involved. It is important that the user employ satisfactory overall system design. It is agreed between the Buyer and Acromag, that this is the Buyer's responsibility.

# 1.0 GENERAL INFORMATION

The Industrial I/O Pack (IP) Series IP330 module is a precision 16-bit, high density, single size IP, with the capability to monitor 16 differential or 32 single-ended analog input channels. The IP330 utilizes state of the art Surface Mounted Technology (SMT) to achieve its high channel density. Four units may be mounted on a carrier board to provide up to 64 differential or 128 single-ended analog input channels per 6U-VMEbus system slot or ISA bus (PC/AT) system slot. The IP330 offers a variety of features which make it an ideal choice for many industrial and scientific applications as described below.

| Model  | Operating Temperature Range |  |

|--------|-----------------------------|--|

| IP330  | 0 to 70°C                   |  |

| IP330E | -40 to 85°C                 |  |

#### **KEY IP330 FEATURES**

- A/D 16-Bit Resolution 16-bit capacitor-based successive approximation Analog to Digital Converter (ADC) with integral sample and hold and reference.

- 8μsec Conversion Time A maximum conversion rate of 125KHz is supported. Maximum recommended conversion rate for specified accuracies is 67KHz.

- High Density Monitors up to 16 differential or 32 singleended analog inputs (acquisition mode and channels are selected via programmable control registers).

- Individual Channel Mail Box Two storage buffer registers are available for each of the 16 differential channels. If configured for 32 single-ended channels, one storage buffer register is available for each of the 32 channels.

- Interrupt Upon Conversion Complete Mode May be programmed to interrupt upon completion of conversion for

- each individual channel or upon completion of conversion of the group of all scanned channels.

- Programmable Control of Channel Scanning Scan all channels or a subset of the channels to allow an overall higher sample rate. The channels digitized include all sequential channels beginning with a specified start-channel value and ending with a specified end-channel value.

- User Programmable Interval Timer Controls the delay between each channel converted when Uniform-Continuous or Single Scan modes are selected. If Burst-Continuous is selected, the Interval Timer controls the delay after a group of channels are converted before conversion is initiated on the group again. Supports a minimum interval of 8µsec and a maximum interval of 2.09 seconds.

- Uniform Continuous Scanning Mode All channels selected for scanning are continually digitized in a round robin fashion with the interval between conversions controlled by the programmed interval timer. The results of each conversion are stored in the channel's corresponding mail box buffer. Scanning is initiated by a software or external trigger. Scanning is stopped by software control.

- Burst Continuous Scanning Mode All selected input scan channels are sequentially digitized at a 67KHz conversion rate (15μ second conversion time). At the end of a programmed interval time a new conversion of all channels is re-initiated. The conversion results are stored in each channel's mail box buffer. This mode can be used as a pseudo-simultaneous sampling mode for low to medium speed applications requiring simultaneous channel acquisition. For example, if four channels are selected then they could be pseudo-simultaneously converted every 60μ seconds (each of the channels actually takes 15μ seconds). This is repeated in bursts determined by the programmed interval time. The scan is initiated by a software or external trigger. Scanning is stopped by software control.

- Uniform Single Cycle Scan Mode All channels selected for scanning are digitized once with the idle time between each channel conversion controlled by the programmed interval timer. The scan is initiated by a software or external trigger.

- Burst Single Cycle Scan Mode All channels selected for scanning are digitized once at a 66.7KHz conversion rate (15µsec/Channel). The scan is initiated by a software or external trigger.

- External Trigger Scan Mode A single channel is digitized

with each external trigger. Successive channels are digitized

in sequential order with each new external trigger. This mode

allows synchronization of conversions with external events

that are often asynchronous.

- External Trigger Output The external trigger is assigned to a field I/O line. This external trigger may be configured as an output signal to provide a means to synchronize other IP330's or devices to a single IP330's on board timer reference.

- User Programmable Gain Amplifier Provides independently software controlled gains (1, 2, 4, and 8V/V) for each of the 16 differential or 32 single-ended channels.

- Precision On Board Calibration Voltages Calibration autozero and autospan precision voltages are available to permit host computer correction of conversion errors.

Trimmed calibration voltages include: 0V (local analog ground), 4,9V, 2,45V, 1,225V, and 0,6125V.

- Hardware DIP Switch For Selection of A/D Ranges Both bipolar (±5V, ±10V) and unipolar (0 to 5V and 0 to 10V) ranges are available. Selected range applies to all channels and can-not be individually selected on a per channel basis.

- New Data Register This register can be polled, to indicate

when new digitized data is available in the mail box. A set bit

indicates a new digitized data value is available in the bit's

corresponding mail box register. Register bits are cleared

upon read of their corresponding mail box register or start of a

new scan cycle.

- Missed Data Register A set bit in the Missed Data register indicates that the last digitized value was not read by the host computer quickly enough and has been overwritten by a new conversion. The Missed Data register has a bit corresponding to each of the 16 differential or 32 single-ended channels. Each Missed Data register bit is cleared by a read of its corresponding mail box data value or start of a new scan cycle.

- User Programmable Data Output Format Software control provides selection of straight binary or binary two's complement data output format.

- Hardware Jumpers For Selection of Internal or External Supply - Hardware jumper provide a means to select internal ±12 volts or external ±15 volt supplies. External supplies are required when using inputs exceeding ±8.5 volts.

- Fault Protected Input Channels Analog input overvoltage protection from -35 V to +55 V is provided in the event of power loss or power off.

#### **INDUSTRIAL I/O PACK INTERFACE FEATURES**

- High density Single-size, industry standard, IP module footprint. Four units mounted on a carrier board provide up to 64 differential or 128 single-ended channels in a single system slot. Both VMEbus and ISA bus (PC/AT) carriers are supported.

- Local ID Each IP module has its own 8-bit ID signature which can be read via access to the ID space.

- 16-bit and 8-bit I/O Port register Read/Write is performed through data transfer cycles in the IP module I/O space.

- High Speed Access times for all data transfer cycles are described in terms of "wait" states 1 wait state is required for reading and writing all control registers and ID values. Interrupt select cycles also require 1 wait state for reading the interrupt vector. Read of the Mail Box buffers typically requires 1 wait state but, to avoid contention with an ongoing memory write cycle, could require from 1 to 6 wait states (see Specifications section for detailed information).

#### SIGNAL INTERFACE PRODUCTS

(See Appendix for more information on compatible products)

This IP module will mate directly to any industry standard IP carrier board. Acromag's AVME9630/9660 3U/6U non-intelligent VMEbus carrier boards and Acromag's APC8600 ISA bus (PC/AT) carrier board are supported. A wide range of other Acromag IP modules are also available to serve your signal conditioning and interface needs.

The cables and termination panels, described in the following paragraphs, are also available. For optimum performance with the 16-bit IP330 analog input module, use of the shortest possible length of shielded input cable is recommended.

\_\_\_\_\_\_

#### Cables

Model 5025-551-X (Shielded Cable): A Flat 50-pin cable with female connectors at both ends for connecting AVME9630/9660, or other compatible carrier boards, to Model 5025-552 termination panels. The "-X" suffix of the model number is used to indicate the length in feet. The shielded cable is highly recommended for optimum performance with the IP330 analog input module.

A shielded cable for the APC8600 ISA bus carrier is not available directly from Acromag but is strongly recommended. The cable is used to mate the high-density (25mil pitch) 50-pin I/O connectors of the APC8600 carrier board to the high-density connectors on the APC8600 Termination Panel. The following vendors' shielded ribbon cable and connector part number information is provided to facilitate construction of your own shielded cables.

**Connector:** The connector is a 50-pin, high-density (25mil pitch), female receptacle header (T&B Ansley Part 311-050302 or equivalent). The connector mates to the male connector (T&B Ansley Part 311-050072E or equivalent) on the APC8600 carrier board at one end of the cable and the APC8600 termination panel at the other end of the cable.

**Cable:** 50-wire flat ribbon cable, 30 gage, Shielded (T&B/Ansley Part 188-050 or equivalent).

#### **Termination Panels:**

Model 5025-552: A DIN-rail mountable panel that provides 50 screw terminals for universal field I/O termination. Connects to Acromag AVME9630/9660, or other compatible carrier boards, via flat 50-pin ribbon cable (Model 5025-551-X).

Model 5029-910 APC8600 High-Density-to-Screw-Terminal Termination Panel: This panel converts the high-density ribbon-cable connectors coming from the APC8600 carrier board to screw terminals, for direct-wired interfaces.

#### **Transition Module:**

Model TRANS-GP: This module repeats field I/O connections of IP modules A through D for rear exit from a VMEbus card cage. It is available for use in card cages which provide rear exit for I/O connections via transition modules (transition modules can only be used in card cages specifically designed for them). It is a double-height (6U), single-slot module with front panel hardware adhering to the VMEbus mechanical dimensions, except for shorter printed circuit board depth. It connects to Acromag Termination Panel 5025-552 from the rear of the card cage, and to AVME9630/9660 boards within the card cage, via flat 50-pin ribbon cable (cable Model 5025-551-X).

# INDUSTRIAL I/O PACK SOFTWARE LIBRARY

Acromag provides an Industrial I/O Pack Software Library diskette (Model IPSW-LIB-M03, MSDOS format) to simplify communication with the board. Example software functions are provided for both VMEbus and ISA bus (PC/AT) applications. All functions are written in the "C" programming language and can be linked to your application. For more details, refer to the "README.TXT" file in the root directory on the diskette and the "INFO330.TXT" file in the appropriate "IP330" subdirectory off of "VMEIP" or "\PCIP", according to your carrier.

## 2.0 PREPARATION FOR USE

#### **UNPACKING AND INSPECTION**

Upon receipt of this product, Inspect the shipping carton for evidence of mishandling during transit. If the shipping carton is badly damaged or water stained, request that the carrier's agent be present when the carton is opened. If the carrier's agent is absent when the carton is opened and the contents of the carton are damaged, keep the carton and packing material for the agent's inspection.

For repairs to a product damaged in shipment, refer to the Acromag Service Policy to obtain return instructions. It is suggested that salvageable shipping cartons and packing material

be saved for future use in the event the product must be shipped.

This board is physically protected with packing material and electrically protected with an anti-static bag during shipment. However, it is recommended that the board be visually inspected for evidence of mishandling prior to applying power.

The board utilizes static sensitive components and should only be handled at a static-safe workstation.

#### **CARD CAGE CONSIDERATIONS**

Refer to the specifications for loading and power requirements. Be sure that the system power supplies are able to accommodate the power requirements of the carrier board, plus the installed IP modules, within the voltage tolerances specified.

IMPORTANT: Adequate air circulation must be provided to prevent a temperature rise above the maximum operating temperature.

The dense packing of the IP modules to the carrier board restricts air flow within the card cage and is cause for concern. Adequate air circulation must be provided to prevent a temperature rise above the maximum operating temperature and to prolong the life of the electronics. If the installation is in an industrial environment and the board is exposed to environmental air, careful consideration should be given to air-filtering.

# **BOARD CONFIGURATION**

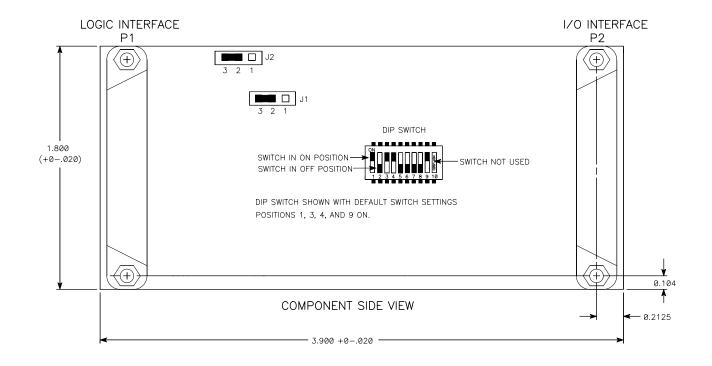

The board may be configured differently, depending on the application. All possible DIP switch and jumper settings will be discussed in the following sections. The DIP switch and jumper locations are shown in Drawing 4501-590.

Remove power from the board when configuring hardware jumpers, installing IP modules, cables, termination panels, and field wiring. Refer to Mechanical Assembly Drawing 4501-434 and the following paragraphs for configuration and assembly instructions.

#### **Default Hardware Jumper Configuration**

When the board is shipped from the factory, it is configured as follows:

- Analog input range is configured for a bipolar input with a 10 volt span (i.e. an ADC input range of -5 to +5 Volts).

- Internal +12 and -12 Volt power supplies are used (sourced from P1 connector).

- The default programmable software control register bits at power-up are described in section 3. The control registers must be programmed to the desired gain, mode, and channel configuration before starting ADC analog input acquisition.

# **Analog Input Range Hardware Jumper Configuration**

The ADC input range is programmed via hardware DIP switch. The DIP switch controls the input voltage span and the selection of unipolar or bipolar input ranges. The configuration of the DIP switch for the different ranges is shown in the following table. A switch selected as "ON" would be positioned to the side of the DIP labeled "ON". The DIP switch location is shown in Drawing 4501-590

Table 2.1: Analog Input Range Selections/DIP Switch Settings

| Desired<br>ADC Input<br>Range*<br>(VDC) | Required<br>Input Span<br>(Volts) | Required<br>Input<br>Type | Switch<br>Settings<br>ON | Switch<br>Settings<br>OFF |

|-----------------------------------------|-----------------------------------|---------------------------|--------------------------|---------------------------|

| -5 to +5                                | 10                                | Bipolar                   | 1,3,4,9                  | 2,5,6,7,8                 |

| -10 to +10**                            | 20                                | Bipolar                   | 2,5,6,9                  | 1,3,4,7,8                 |

| 0 to +5                                 | 5                                 | Unipolar                  | 1,3,5,8                  | 2,4,6,7,9                 |

| 0 to +10**                              | 10                                | Unipolar                  | 1,3,4,7                  | 2,5,6,8,9                 |

<sup>\*</sup> Assuming a gain of 1.

#### **Power Supply Hardware Jumper Configuration**

The selection of internal or external analog power supplies is accomplished via hardware jumpers J1 and J2. J1 (J2) controls the selection of either the internal +12 (-12) Volt supply sourced from P1 connector, or the external +15 (-15) Volt supply sourced from the P2 connector. The configuration of the jumpers for the different supplies is shown in Table 2.2. "IN" means that the pins are shorted together with a shorting clip. "OUT" means that the clip has been removed. The jumper locations are shown in Drawing 4501-590.

Table 2.2: Power Supply Selections (Pins of J1 and J2)

| rabio 2:2: 1 off of capping colocitons (1 mis of of and o2) |       |       |       |       |

|-------------------------------------------------------------|-------|-------|-------|-------|

| Power Supply                                                | J1    | J1    | J2    | J2    |

| Selection*                                                  | (1&2) | (2&3) | (1&2) | (2&3) |

| ±12 Volt (Internal, P1)                                     | OUT   | IN    | OUT   | IN    |

| ±15 Volt (External, P2)                                     | IN    | OUT   | IN    | OUT   |

<sup>\*</sup> Internal and external supplies should not be mixed (e.g. do not use +12 Volts with -15 Volts).

# **Software Configuration**

Software configurable control registers are provided for control of external trigger mode, data output format, acquisition mode, timer control, interrupt mode, convert channel(s) selection, and channel gain selection. No hardware jumpers are required for

control of these functions. These control registers must also be configured as desired before starting ADC analog input acquisition. Refer to section 3 for programming details.

#### **CONNECTORS**

#### IP Field I/O Connector (P2)

P2 provides the field I/O interface connections for mating IP modules to the carrier board. P2 is a 50-pin female receptacle header (AMP 173279-3 or equivalent) which mates to the male connector of the carrier board (AMP 173280-3 or equivalent). This provides excellent connection integrity and utilizes gold-plating in the mating area. Threaded metric M2 screws and spacers are supplied with the module to provide additional stability for harsh environments (see Mechanical Assembly Drawing 4501-434). The field and logic side connectors are keyed to avoid incorrect assembly.

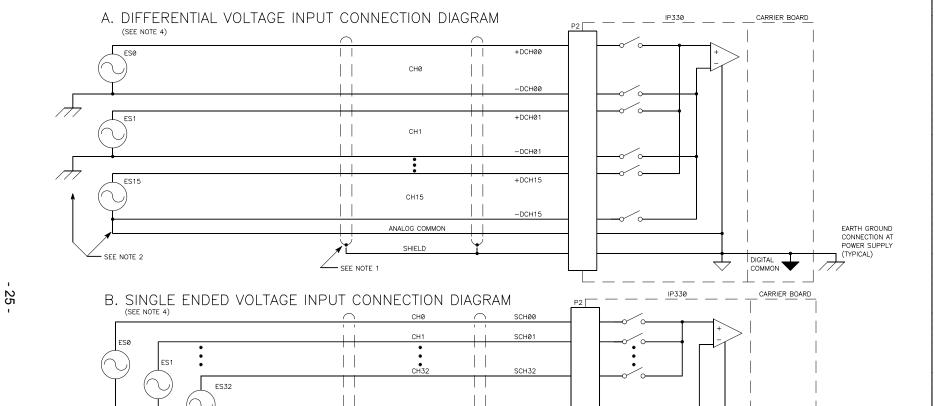

P2 pin assignments are unique to each IP model (see Table 2.3) and normally correspond to the pin numbers of the field I/O interface connector on the carrier board (you should verify this for your carrier board). When reading Table 2.3 note that channel designations are abbreviated to save space. For example, single ended channel 0 is abbreviated as "S00"; the +input for differential channel 0 is abbreviated as "D00+". Both of these labels are attached to pin 1, but only one is active for a particular installation (i.e. if your inputs are applied differentially, which is recommended for the lowest noise and best accuracy, follow the differential channel labeling for each channel's + and - input leads).

IMPORTANT: All unused analog input pins should be tied to analog gorund. Floating unused inputs can drift outside the input range causing temporary saturation of the input analog circuits. Recovery from saturation is slow and affects the reading of the desired channels.

Table 2.3: IP330 Field I/O Pin Connections (P2)

| Pin Description | Number | Pin Description | Number |

|-----------------|--------|-----------------|--------|

| S00,D00+        | 1      | S24,D08-        | 26     |

| S16,D00-        | 2      | COMMON          | 27     |

| COMMON          | 3      | S09,D09+        | 28     |

| S01,D01+        | 4      | S25,D09-        | 29     |

| S17,D01-        | 5      | COMMON          | 30     |

| COMMON          | 6      | S10,D10+        | 31     |

| S02,D02+        | 7      | S26,D10-        | 32     |

| S18,D02-        | 8      | COMMON          | 33     |

| COMMON          | 9      | S11,D11+        | 34     |

| S03,D03+        | 10     | S27,D11-        | 35     |

| S19,D03-        | 11     | COMMON          | 36     |

| COMMON          | 12     | S12,D12+        | 37     |

| S04,D04+        | 13     | S28,D12-        | 38     |

| S20,D04-        | 14     | COMMON          | 39     |

| COMMON          | 15     | S13,D13+        | 40     |

| S05,D05+        | 16     | S29,D13-        | 41     |

| S21,D05-        | 17     | SENSE           | 42     |

| COMMON          | 18     | S14,D14+        | 43     |

| S06,D06+        | 19     | S30,D14-        | 44     |

| S22,D06-        | 20     | +15 VOLTS       | 45     |

| COMMON          | 21     | S15,D15+        | 46     |

| S07,D07+        | 22     | S31,D15-        | 47     |

| S23,D07-        | 23     | -15 VOLTS       | 48     |

| COMMON          | 24     | EXT TRIGGER*    | 49     |

| S08,D08+        | 25     | SHIELD          | 50     |

<sup>\*</sup> Indicates that the signal is active low.

<sup>\*\*</sup> These ranges can only be achieved with ±15V external power supplies. The input ranges will be clipped if ±12V supplies are used, typically to ±8.5 V maximum inputs.

#### **Analog Inputs: Noise and Grounding Considerations**

Differential inputs require two leads (+ and -) per channel, and provide rejection of common mode voltages. This allows the desired signal to be accurately measured. However, the signal being measured cannot be floating—it must be referenced to analog common on the IP module and be within the normal input voltage range.

Differential inputs are the best choice when the input channels are sourced from different locations having slightly different ground references and when minimizing noise and maximizing accuracy are key concerns. See Drawing 4501-591 for analog input connections for differential and single-ended inputs. Shielded cable of the shortest length possible is also strongly recommended.

Single-ended inputs only require a single lead (+) per channel, with a shared "sense" (reference) lead for all channels, and can be used when a large number of input channels come from the same location (e.g. printed circuit board). The channel density doubles when using single-ended inputs, and this a powerful incentive for their use. However, caution must be exercised since the single "sense" lead references all channels to the same common which will induce noise and offset to the degree they are different.

The IP330 is non-isolated, since there is electrical continuity between the logic and field I/O grounds. As such, the field I/O connections are not isolated from the carrier board and backplane. Care should be taken in designing installations without isolation to avoid noise pickup and ground loops caused by multiple ground connections. This is particularly important for analog inputs when a high level of accuracy/resolution is needed. Contact your Acromag representative for information on our many isolated signal conditioning products that could be used to interface to the IP330 input module.

## **External Trigger Input/Output**

The external trigger signal on pin 49 of the P2 connector can be programmed to input a TTL compatible external trigger signal, or output IP330 hardware generated triggers to allow synchronization of multiple IP330s.

As an input, the external trigger must be a 5 Volt logic, TTL-compatible, debounced signal referenced to analog common. The external trigger signal is an active low edge sensitive signal. That is, the external trigger signal will trigger the IP330 hardware on the falling edge. Once the external trigger signal has been driven low, it should remain low for a minimum of 500n seconds.

As an output an active-low TTL signal can be driven to additional IP330s, thus providing a means to synchronize the conversions of multiple IP330s. The additional IP330s must program their external trigger for signal input and convert on external trigger only mode. See section 3.0 for programming details to make use of this signal.

# IP Logic Interface Connector (P1)

P1 of the IP module provides the logic interface to the mating connector on the carrier board. This connector is a 50-pin female receptacle header (AMP 173279-3 or equivalent) which mates to the male connector of the carrier board (AMP 173280-3 or

equivalent). This provides excellent connection integrity and utilizes gold-plating in the mating area. Threaded metric M2 screws and spacers are supplied with the IP module to provide additional stability for harsh environments (see Drawing 4501-434 for assembly details). Field and logic side connectors are keyed to avoid incorrect assembly. The pin assignments of P1 are standard for all IP modules according to the Industrial I/O Pack Specification (see Table 2.4).

Table 2.4: Standard Logic Interface Connections (P1)

| Pin Description | Number | Pin Description | Number |

|-----------------|--------|-----------------|--------|

| GND             | 1      | GND             | 26     |

| CLK             | 2      | +5V             | 27     |

| Reset*          | 3      | R/W*            | 28     |

| D00             | 4      | IDSEL*          | 29     |

| D01             | 5      | DMAReq0*        | 30     |

| D02             | 6      | MEMSEL*         | 31     |

| D03             | 7      | DMAReq1*        | 32     |

| D04             | 8      | IntSel*         | 33     |

| D05             | 9      | DMAck0*         | 34     |

| D06             | 10     | IOSEL*          | 35     |

| D07             | 11     | RESERVED        | 36     |

| D08             | 12     | A1              | 37     |

| D09             | 13     | DMAEnd*         | 38     |

| D10             | 14     | A2              | 39     |

| D11             | 15     | ERROR*          | 40     |

| D12             | 16     | A3              | 41     |

| D13             | 17     | INTReq0*        | 42     |

| D14             | 18     | A4              | 43     |

| D15             | 19     | INTReq1*        | 44     |

| BS0*            | 20     | A5              | 45     |

| BS1*            | 21     | STROBE*         | 46     |

| -12V            | 22     | A6              | 47     |

| +12V            | 23     | ACK*            | 48     |

| +5V             | 24     | RESERVED        | 49     |

| GND             | 25     | GND             | 50     |

An Asterisk (\*) is used to indicate an active-low signal. **BOLD ITALIC** Logic Lines are NOT USED by this IP Model.

# 3.0 PROGRAMMING INFORMATION

# IP IDENTIFICATION PROM - (Read Only, 32 Odd-Byte Addresses)

Each IP module contains an identification (ID) information that resides in the ID space per the IP module specification. This area of memory contains 32 bytes of information at most. Both fixed and variable information may be present within the ID space. Fixed information includes the "IPAC" identifier, model number. and manufacturer's identification codes. Variable information includes unique information required for the module. The IP330 ID information does not contain any variable (e.g. unique calibration) information. ID space bytes are addressed using only the odd addresses in a 64 byte block (on the "Big Endian" VMEbus). Even addresses are used on the "Little Endian" PC ISA bus. The IP330 ID space contents are shown in Table 3.1. Note that the baseaddress for the IP module ID space (see your carrier board instructions) must be added to the addresses shown to properly access the ID space. Execution of an ID space read requires 1 wait state.

Table 3.1: IP330 ID Space Identification (ID) PROM

| Hex Offset<br>From ID<br>PROM Base<br>Address | ASCII<br>Character<br>Equivalent | Numeric<br>Value<br>(Hex) | Field Description          |

|-----------------------------------------------|----------------------------------|---------------------------|----------------------------|

| 01                                            | I                                | 49                        | All IP's have 'IPAC'       |

| 03                                            | Р                                | 50                        |                            |

| 05                                            | Α                                | 41                        |                            |

| 07                                            | С                                | 43                        |                            |

| 09                                            |                                  | A3                        | Acromag ID Code            |

| 0B                                            |                                  | 11                        | IP Model Code <sup>1</sup> |

| 0D                                            |                                  | 00                        | Not Used                   |

|                                               |                                  |                           | (Revision)                 |

| 0F                                            |                                  | 00                        | Reserved                   |

| 11                                            |                                  | 00                        | Not Used (Driver           |

|                                               |                                  |                           | ID Low Byte)               |

| 13                                            |                                  | 00                        | Not Used (Driver           |

|                                               |                                  |                           | ID High Byte)              |

| 15                                            |                                  | 0C                        | Total Number of            |

|                                               |                                  |                           | ID PROM Bytes              |

| 17                                            |                                  | 5A                        | CRC                        |

| 19 to 3F                                      |                                  | уу                        | Not Used                   |

# Notes (Table 3.1):

1. The IP model number is represented by a two-digit code within the ID space (the IP330 model is represented by 11 Hex).

#### I/O SPACE ADDRESS MAP

This board is addressable in the Industrial Pack I/O space to control the acquisition of analog inputs from the field. As such, three types of information are stored in the I/O space: control, status, and data.

The I/O space may be as large as 64, 16-bit words (128 bytes) using address lines A1 to A6, but the IP330 uses only a portion of this space. The I/O space address map for the IP330 is shown in Table 3.2. Note that the base address for the IP module I/O space (see your carrier board instructions) must be added to the addresses shown to properly access the I/O space. Both 16 and 8-bit accesses to the registers in the I/O space are permitted.

Table 3.2: IP330 I/O Space Address (Hex) Memory Map<sup>2</sup>

| Base  | MSB             | SB LSB                    |       |  |

|-------|-----------------|---------------------------|-------|--|

| Addr+ | D15 D08         | D07 D00                   | Addr+ |  |

| 00    | Control         | Register                  |       |  |

|       |                 |                           | 01    |  |

| 02    | Timer Prescaler | Interrupt Vector          |       |  |

|       |                 |                           | 03    |  |

| 04    | Convers         | ion Timer                 |       |  |

|       |                 |                           | 05    |  |

| 06    | End Channel     | End Channel Start Channel |       |  |

|       | Value Value     |                           | 07    |  |

| 08    | New Data        | New Data Register         |       |  |

|       | Channel         | Channels 0 to 15          |       |  |

| 0A    | New Data        | New Data Register         |       |  |

|       | Channels        | 0B                        |       |  |

| 0C    | Missed Da       |                           |       |  |

|       | Channel         | 0D                        |       |  |

| 0E    | Missed Da       | Missed Data Register      |       |  |

|       | Channels        | s 16 to 31                | 0F    |  |

| Base     | MSB                                    |                   | LSB             | Base     |

|----------|----------------------------------------|-------------------|-----------------|----------|

| Addr+    | D15 D08                                | D07               |                 | Addr+    |

| 10       | Not Used                               |                   | Start Convert   | 710011   |

|          | Bits15 to Bit 01                       |                   | Bit-0           | 11       |

| 12       | Not                                    | Used <sup>1</sup> |                 | 13       |

|          |                                        | <del> </del>      |                 |          |

| 1E       | Not                                    | Used <sup>1</sup> |                 | 1F       |

| 20       | Gain Select Ch 00                      | Ga                | in Select Ch 01 | 21       |

| 22       | Gain Select Ch 02                      |                   | in Select Ch 03 | 23       |

| 24       | Gain Select Ch 04                      |                   | in Select Ch 05 | 25       |

| 26       | Gain Select Ch 06                      | Ga                | in Select Ch 07 | 27       |

| 28       | Gain Select Ch 08                      | Ga                | in Select Ch 09 | 29       |

| 2A       | Gain Select Ch 10                      | Ga                | in Select Ch 11 | 2B       |

| 2C       | Gain Select Ch 12                      | Ga                | in Select Ch 13 | 2D       |

| 2E       | Gain Select Ch 14                      | Ga                | in Select Ch 15 | 2F       |

| 30       | Gain Select Ch 16                      | Ga                | in Select Ch 17 | 31       |

| 32       | Gain Select Ch 18                      |                   | in Select Ch 19 | 33       |

| 34       | Gain Select Ch 20                      |                   | in Select Ch 21 | 35       |

| 36       | Gain Select Ch 22                      |                   | in Select Ch 23 | 37       |

| 38       | Gain Select Ch 24                      |                   | in Select Ch 25 | 39       |

| 3A       | Gain Select Ch 26                      |                   | in Select Ch 27 | 3B       |

| 3C       | Gain Select Ch 28                      |                   | in Select Ch 29 | 3D       |

| 3E       | Gain Select Ch 30                      |                   | in Select Ch 31 | 3F       |

| 40       | Mail Box Ch 00                         |                   |                 | 41       |

| 42       | Mail Box Ch 01                         |                   |                 | 43       |

| 44       | Mail Box Ch 02                         |                   |                 | 45       |

| 46<br>48 | Mail Box Ch 03                         |                   |                 | 47<br>49 |

| 46<br>4A | Mail Box Ch 04<br>Mail Box Ch 05       | (SE or            | Diff. Mode)     | 49<br>4B |

| 4C       | Mail Box Ch 06                         |                   |                 | 4D       |

| 4E       | Mail Box Ch 07                         |                   |                 | 4F       |

| 50       | Mail Box Ch 08                         |                   |                 | 51       |

| 52       | Mail Box Ch 09                         |                   |                 | 53       |

| 54       | Mail Box Ch 10                         |                   |                 | 55       |

| 56       | Mail Box Ch 11                         |                   |                 | 57       |

| 58       | Mail Box Ch 12                         |                   |                 | 59       |

| 5A       | Mail Box Ch 13                         |                   |                 | 5B       |

| 5C       | Mail Box Ch 14                         |                   |                 | 5D       |

| 5E       | Mail Box Ch 15                         |                   |                 | 5F       |

| 60       | Mail Box Ch 16 SE                      |                   |                 | 61       |

| 62       | Mail Box Ch 17 SE                      |                   |                 | 63       |

| 64       | Mail Box Ch 18 SE                      | _ `               |                 | 65       |

| 66       | Mail Box Ch 19 SE                      | _ `               |                 | 67       |

| 68       | Mail Box Ch 20 SE                      |                   |                 | 69       |

| 6A       | Mail Box Ch 21 SE                      | - :               |                 | 6B       |

| 6C<br>6E | Mail Box Ch 22 SE                      |                   |                 | 6D<br>6F |

| 70       | Mail Box Ch 23 SE<br>Mail Box Ch 24 SE |                   |                 | 71       |

| 70       | Mail Box Ch 25 SE                      |                   |                 | 73       |

| 74       | Mail Box Ch 26 SE                      | (Ch               | 10 Diff Mode)   | 75       |

| 76       | Mail Box Ch 27 SE                      |                   |                 | 77       |

| 78       | Mail Box Ch 28 SE                      |                   |                 | 79       |

| 7A       | Mail Box Ch 29 SE                      |                   |                 | 7B       |

| 7C       | Mail Box Ch 30 SE                      |                   |                 | 7D       |

| 7E       | Mail Box Ch 31 SE                      |                   |                 | 7F       |

|          |                                        | _                 |                 |          |

# Notes (Table 3.2):

- 1. The IP will not respond to addresses that are "Not Used".

- All Reads and writes are 1 wait state (except a Mail Box read issued simultaneously with an ongoing hardware write of a new convert value. In this case a read cycle will include from 1 to 6 wait states).

- 3. The Mail Box is one level deep when using single ended channels; it is two levels deep with differential mode.

This memory map reflects byte accesses using the "Big Endian" byte ordering format. Big Endian is the convention used in the Motorola 68000 microprocessor family and is the VMEbus convention. In Big Endian, the lower-order byte is stored at odd-byte addresses. The Intel x86 family of microprocessors uses the opposite convention, or "Little Endian" byte ordering. Little Endian uses even-byte addresses to store the low-order byte. As such, installation of this module on a PC carrier board will require the use of the even address locations to access the lower 8-bit data while on a VMEbus carrier use of odd address locations are required to access the lower 8-bit data.

#### Control Register, (Read/Write) - (Base + 00H)

This read/write register is used to: select the output data format, select the external trigger signal as an input or output, select acquisition input mode, select scan mode, enable/disable the timer, and select the interrupt mode.

The function of each of the control register bits are described in Table 3.3. This register can be read or written with either 8-bit or 16-bit data transfers. A power-up or system reset sets all control register bits to 0.

Table 3.3: Control Register

| BIT      | FUNCTION                                                                                            |

|----------|-----------------------------------------------------------------------------------------------------|

| 0        | Not Used <sup>1</sup>                                                                               |

| 1        | Output Data Format                                                                                  |

|          | 0 = Binary Two's Complement                                                                         |

|          | 1 = Straight Binary                                                                                 |

|          | See Tables 3.4 and 3.5 for a description of these                                                   |

|          | two data formats.                                                                                   |

| 2        | External Trigger                                                                                    |

|          | 0 = Input                                                                                           |

|          | 1 = Output                                                                                          |

|          | It is possible to synchronize the data acquisition of                                               |

|          | multiple IP330 modules. A single master IP330                                                       |

|          | module must be selected to output the external                                                      |

|          | trigger signal while all other IP330 modules are selected to input the external trigger signal. The |

|          | external trigger signal (pin 49 of the field I/O                                                    |

|          | connector) must also be wired together.                                                             |

| 5,4,3    | Acquisition Input Mode                                                                              |

| 0,4,0    | 000 = All Channels Differential Input                                                               |

|          | 001 = All Channels Single Ended Input                                                               |

|          | 010 = Not Used                                                                                      |

|          | 011 = 4.9000v Calibration Voltage Input                                                             |

|          | 100 = 2.4500v Calibration Voltage Input                                                             |

|          | 101 = 1.2250v Calibration Voltage Input                                                             |

|          | 110 = 0.6125v Calibration Voltage Input                                                             |

|          | 111 = Auto Zero Calibration Voltage Input                                                           |

| 7,6      | Not Used <sup>1</sup>                                                                               |

| 10,9,8   | Scan Mode                                                                                           |

|          | 000 = Disable                                                                                       |

|          | 001 = Uniform Continuous                                                                            |

|          | 010 = Uniform Single                                                                                |

|          | 011 = Burst Continuous                                                                              |

|          | 100 = Burst Single<br>101 = Convert on External Trigger Only                                        |

|          | 110 = Not Used                                                                                      |

|          | 111 = Not Used                                                                                      |

|          | See the Modes of Operation section for a                                                            |

|          | description of each of these scan modes.                                                            |

| <u> </u> | p                                                                                                   |

| BIT   | FUNCTION                                        |  |

|-------|-------------------------------------------------|--|

| 11    | Timer Enable                                    |  |

|       | 0 = Disable                                     |  |

|       | 1 = Enable                                      |  |

| 13,12 | Interrupt Control                               |  |

|       | 00 = Disable Interrupts                         |  |

|       | 01 = Interrupt After Convert of Each Channel    |  |

|       | 10 = Interrupt After Conversion of all selected |  |

|       | channels is completed. A group of channels      |  |

|       | includes all channels from the Start Channel up |  |

|       | to and including the End Channel value.         |  |

|       | 11 = Disable Interrupts                         |  |

| 14,15 | Not Used <sup>1</sup>                           |  |

#### Notes (Table 3.3):

All bits labeled "Not Used" will return on a read access the last value written.

#### **Analog Input Ranges and Corresponding Digital Output Code**

Selection of an analog input range is implemented via the DIP switch setting given in Table 2.1. The ideal input voltage corresponding to each of the supported input ranges is given in Table 3.4. Then in Table 3.5 the digital output code corresponding to each of the given ideal analog input values is given in both binary two's complement and straight binary formats.

Table 3.4: Supported Full-Scale Ranges and Ideal Analog Input

| DESCRIPTION                              |          | ANALO    | G INPUT  |          |

|------------------------------------------|----------|----------|----------|----------|

| Input Range                              | ±10V     | 0 to 10V | ±5V      | 0 to 5V  |

| LSB (Least<br>Significant Bit)<br>Weight | 305μV    | 153μV    | 153μV    | 76μV     |

| + Full Scale                             | 9.999695 | 9.999847 | 4.999847 | 4.999924 |

| Minus One LSB                            | Volts    | Volts    | Volts    | Volts    |

| Midscale                                 | 0V       | 5V       | 0V       | 2.5V     |

| One LSB Below                            | -305μV   | 4.999847 | -153μV   | 2.499924 |

| Midscale                                 |          | Volts    |          | Volts    |

| - Full Scale                             | -10V     | 0V       | -5V      | 0V       |

The digital output format is controlled by bit-1 of the Control register. The two formats supported are Binary Two's Complement and Straight Binary. The hex codes corresponding to these two data formats are depicted in Table 3.5.

Table 3.5: Digital Output Codes and Input Voltages

|                      | DIGITAL (                      | DUTPUT     |  |  |

|----------------------|--------------------------------|------------|--|--|

|                      | Binary 2's Comp Straight Binar |            |  |  |

| DESCRIPTION          | (Hex Code)                     | (Hex Code) |  |  |

| + Full Scale - 1 LSB | 7FFF                           | FFFF       |  |  |

| Midscale             | 0000                           | 8000       |  |  |

| 1 LSB Below Midscale | FFFF                           | 7FFF       |  |  |

| - Full Scale         | 8000                           | 0000       |  |  |

## Interrupt Vector Register (Read/Write, 03H)

The Vector Register can be written with an 8-bit interrupt vector. This vector is provided to the carrier and system bus upon an active INTSEL\* cycle. Read or writing to this register is

possible via 16-bit or 8-bit data transfers. 16-bit data transfers will implement simultaneous access the Interrupt Vector and Timer Prescaler registers. The register contents are cleared upon reset.

| Interrupt Vector Register |    |    |    |    |    |    |     |

|---------------------------|----|----|----|----|----|----|-----|

| MSB                       |    |    |    |    |    |    | LSB |

| 07                        | 06 | 05 | 04 | 03 | 02 | 01 | 00  |

Interrupts are released on an interrupt acknowledge cycle. Read of the interrupt vector during an interrupt acknowledge cycle signals the IP330 to remove its interrupt request.

#### Timer Prescaler Register (Read/Write, 02H)

The Timer Prescaler register can be written with an 8-bit value to control the interval time between conversions.

| Timer Prescaler Register |    |    |    |    |    |    |     |  |

|--------------------------|----|----|----|----|----|----|-----|--|

| MSB                      |    |    |    |    |    |    | LSB |  |

| 15                       | 14 | 13 | 12 | 11 | 10 | 09 | 80  |  |

This 8-bit number divides an 8 MHz clock signal. The clock signal is further divided by the number held in the Conversion Timer Register. The resulting frequency can be used to generate periodic triggers for precisely timed intervals between conversions.

The Timer Prescaler has a minimum allowed value restriction of 40 hex or 64 decimal. A Timer Prescaler value of less then 64 (decimal) will result in an empty Mail Box Register buffer. This minimum value corresponds to a conversion interval of  $8\mu$  seconds which translates to the maximum conversion rate of 125KHz. Although the board will operate at the 125KHz conversion rate, conversion accuracy will be sacrificed.

The formula used to calculate and determine the desired Timer Prescaler value is given in the Conversion Timer section which immediately follows this section.

Read or writing to this register is possible via 16-bit or 8-bit data transfers. A 16-bit data transfer will implement simultaneous access to the Interrupt Vector and Timer Prescaler registers. The Timer Prescaler register contents are cleared upon reset.

#### Conversion Timer Register (Read/Write, 04H)

The Conversion Timer Register can be written to control the interval time between conversions. Read or writing to this register is possible with either 16-bit or 8-bit data transfers. This register's contents are cleared upon reset.

|    | Conversion Timer Register |    |    |    |    |       |                      |    |

|----|---------------------------|----|----|----|----|-------|----------------------|----|

| MS | В                         |    |    |    |    |       | L                    | SB |

| 15 | 14                        | 13 | 12 | 11 | 10 | 09 08 | 07 06 05 04 03 02 01 | 00 |

This 16-bit number is the second divisor of an 8MHz. clock signal and is used together with the Timer Prescaler Register to derive the frequency of periodic triggers for precisely timed intervals between conversions.

The interval time between conversion triggers is generated by cascading two counters. The first counter, the Timer Prescaler, is clocked by an 8MHz. clock signal. The output of this clock is input

to the second counter, the Conversion Timer, and the output is used to generate periodic trigger pulses. The time period between trigger pulses is described by the following equation:

$$\frac{Timer\ Prescaler *\ Conversion\ Timer}{8} = T\ in\ \mu\ seconds$$

Where: **T** = time period between trigger pulses in microseconds. **Timer Prescaler** can be any value between 64 and 255 decimal

**Conversion Timer** can be any value between 1 and 65.535 decimal.

The maximum period of time which can be programmed to occur between conversions is  $(255*65,535) \div 8 = 2.0889$  seconds. The minimum time interval which can be programmed to occur is

$(64*1) \div 8 = 8\mu$  seconds. This minimum of  $8\mu$  seconds is defined by the minimum conversion time of the hardware but does sacrifice conversion accuracy. To achieve specified conversion accuracy a minimum conversion time of  $15\mu$  seconds is recommended (see the specification chapter for details regarding accuracy).

#### Start Channel Value Register (Read/Write, 07H)

The Start Channel Value register can be written with a 5-bit value to select the first channel that is to be converted once conversions have been triggered. All channels between the start and end channel values are converted. A single channel can be selected by writing the desired channel value in both the Start and End Channel Value registers.

The Start Channel Value register can be read or written with 8-bit data transfers. In addition, the Start Channel Value register can be simultaneously accessed with the End Channel Value via a 16-bit data transfer. The unused bits are zero when read. The register contents are cleared upon reset.

| Start Channel Value Register |    |         |         |       |    |  |  |

|------------------------------|----|---------|---------|-------|----|--|--|

| Unused                       |    | Start ( | Channel | Value |    |  |  |

| 07 06 05                     | 04 | 03      | 02      | 01    | 00 |  |  |

After running data conversions are halted, the internal hardware pointers are reinitialized to the start channel value. Thus when conversions are started again, the first channel converted is defined by the Start Channel Value register.

# End Channel Value Register (Read/Write, 06H)

The End Channel Value register can be written with a 5-bit value to indicate the last channel in a sequence to be converted. When scanning, all channels between and including the start and end channels are converted. A single channel can be selected by writing the desired channel value in both the Start and End Channel Value registers.

The End Channel Value register can be read or written with 8-bit data transfers. In addition, the End Channel Value register can be simultaneously accessed with the Start Channel Value with a 16-bit data transfer. The unused data bits are zero when read. The register contents are cleared upon reset.

| End Channel Value Register |             |       |           |       |    |  |  |

|----------------------------|-------------|-------|-----------|-------|----|--|--|

| Unused                     |             | End C | Channel ' | Value |    |  |  |

| 15 14 13                   | 12 11 10 09 |       |           |       | 80 |  |  |

#### New Data Registers (Read Only, 08H to 0BH)

The New Data registers can be read to determine which channels of the Mail Box buffer contain new converted data. A set bit in the New Data register indicates that the Mail Box buffer, corresponding to the channel of the set bit, contains new converted data. A set New Data register bit is cleared upon a read of its corresponding Mail Box buffer.

The New Data bits are also cleared at the start of all new data acquisition cycles initiated with either the Software Start Convert command or an external trigger. This is done to avoid mistaking data from an old scan cycle with that of a new scan cycle.

The New Data registers can be read via 16-bit or 8-bit data transfers. In addition, the register contents are cleared upon reset.

| New                               | New Data Register (Read Only, 09H) |       |         |        |        |     |    |    |  |

|-----------------------------------|------------------------------------|-------|---------|--------|--------|-----|----|----|--|

| Data Bit                          | 07                                 | 06    | 05      | 04     | 03     | 02  | 01 | 00 |  |

| SE or Diff. Ch. I                 | 07                                 | 06    | 05      | 04     | 03     | 02  | 01 | 00 |  |

| Nev                               | v Data                             | Regi  | ster (F | Read ( | Only 0 | 8H) |    |    |  |

| Data Bit                          | 15                                 | 14    | 13      | 12     | 11     | 10  | 09 | 80 |  |

| SE or Diff. Ch.                   | 15                                 | 14    | 13      | 12     | 11     | 10  | 09 | 80 |  |

| New Data Register (Read Only 0BH) |                                    |       |         |        |        |     |    |    |  |

| Data Bit                          | 07                                 | 06    | 05      | 04     | 03     | 02  | 01 | 00 |  |

| SE Channel                        | 23                                 | 22    | 21      | 20     | 19     | 18  | 17 | 16 |  |

| Diff. Channel                     | 07                                 | 06    | 05      | 04     | 03     | 02  | 01 | 00 |  |

| Nev                               | / Data                             | Regis | ster (F | Read ( | Only 0 | AH) |    |    |  |

| Data Bit                          | 15                                 | 14    | 13      | 12     | 11     | 10  | 09 | 80 |  |

| SE Channel                        | 31                                 | 30    | 29      | 28     | 27     | 26  | 25 | 24 |  |

| Diff. Channel                     | 15                                 | 14    | 13      | 12     | 11     | 10  | 09 | 80 |  |

# Missed Data Registers (Read Only, 0CH to 0FH)

The Missed Data registers can be read to determine if a channel's Mail Box buffer has been overwritten with new converted data before the last converted value was read. A set bit in the Missed Data register indicates a converted value corresponding to the channel of the set bit was overwritten before being read. A set Missed Data register bit is cleared upon a read of its corresponding Mail Box buffer.

The Missed Data bits are also cleared at the start of all new data acquisition cycles initiated with either the Software Start Convert command or an external trigger. This is done to avoid mistaking missed data from an old scan cycle with that of a new scan cycle.

The Missed Data registers can be read via 16-bit or 8-bit data transfers. In addition, the register contents are cleared upon reset.

| Misse                                | ed Dat | a Reg | ister ( | Read | Only, | 0DH) |    |    |

|--------------------------------------|--------|-------|---------|------|-------|------|----|----|

| Data Bit                             | 07     | 06    | 05      | 04   | 03    | 02   | 01 | 00 |

| SE or Diff. Ch.                      | 07     | 06    | 05      | 04   | 03    | 02   | 01 | 00 |

| Missed Data Register (Read Only 0CH) |        |       |         |      |       |      |    |    |

| Data Bit                             | 15     | 14    | 13      | 12   | 11    | 10   | 09 | 80 |

| SE or Diff. Ch.                      | 15     | 14    | 13      | 12   | 11    | 10   | 09 | 08 |

| Missed Data Register (Read Only 0FH) |                                      |    |    |    |    |    |    |    |  |

|--------------------------------------|--------------------------------------|----|----|----|----|----|----|----|--|

| Data Bit                             | 07                                   | 06 | 05 | 04 | 03 | 02 | 01 | 00 |  |

| SE Channel                           | 23                                   | 22 | 21 | 20 | 19 | 18 | 17 | 16 |  |

| Diff. Channel                        | 07                                   | 06 | 05 | 04 | 03 | 02 | 01 | 00 |  |

| Miss                                 | Missed Data Register (Read Only 0EH) |    |    |    |    |    |    |    |  |

| Data Bit                             | 15                                   | 14 | 13 | 12 | 11 | 10 | 09 | 80 |  |

| SE Channel                           | 31                                   | 30 | 29 | 28 | 27 | 26 | 25 | 24 |  |

| Diff. Channel                        | 15                                   | 14 | 13 | 12 | 11 | 10 | 09 | 80 |  |

#### Start Convert Register (Write Only, 11H)

The Start Convert register is a write-only register and is used to trigger conversions by setting data bit-0 of this register to a logic one. The desired mode of data acquisition must first be configured by setting the following registers to the desired values and modes: Control, Interrupt Vector, Timer Prescaler, Conversion Timer, Start Channel Value, End Channel Value, and Gain Select.

This register can be written with either a 16-bit or 8-bit data value. Data bit-0 must be a logic one to initiate data conversions.

For the External Trigger Only mode the Software Start Convert bit is not used to start data acquisition. However, the Start Convert bit should be set prior to the first external trigger. In this mode the Start Convert bit serves as a means for the hardware to identify the occurrence of the first External Trigger. On the first external trigger (given the Software Start Convert bit is set) converted data from the A/D Converter is not written to the Mail Box buffer since it is old convert data. See the Convert On External Trigger Only-Mode (in the Modes of Opertion section) for additional details.

|   | Start Convert Register |  |  |  |  |  |  |               |

|---|------------------------|--|--|--|--|--|--|---------------|

| I | Not Used               |  |  |  |  |  |  | Start Convert |

|   | 07 06 05 04 03 02 01   |  |  |  |  |  |  | 00            |

At least  $5\mu$  seconds of data acquire time should be provided after programming of the Control register, Start Value register, and Gain Selects before a Software Start Convert command is issued. These configuration registers control the IP330 on board multiplexers and programmable gain amplifier which, respectively, control the channel and gain selected for the input provided to the converter.

#### Gain Select Registers (Read/Write, 20H - 3FH)

The Gain Select registers are read/writeable and are used to individually select the gain corresponding to each of the 32 channels. The Gain Select registers are the only registers in the IP330 that must be accessed via byte transfers only. See Table 3.2 which lists the Gain Select register addresses corresponding to each of the 32 channels. In differential mode, Gain Select registers corresponding to channels 0 to 15 are utilized.

The four gain settings supported (1, 2, 4, and 8) are listed in Table 3.6 with their correspond binary select code. A gain can be selected by writing the desired binary code to the least significant two bits of a given Gain Select register.

Table 3.6: Gain Select Binary Codes

| Gain | Data Bits 7 to 2 | Data Bit 1 | Data Bit 0 |

|------|------------------|------------|------------|

| 1    | Unused           | 0          | 0          |

| 2    | Unused           | 0          | 1          |

| 4    | Unused           | 1          | 0          |

| 8    | Unused           | 1          | 1          |

The Gain Select register contents are undefined upon power up or system reset. The Gain Select registers corresponding to all channels selected for conversion must be written with the desired gain select binary codes prior to initializing data conversions.

#### Mail Box Buffer (Read Only, 40H - 7EH)

The Mail Box Buffer is read-only, and contains 16-bit digitized input channel values. The Mail Box Buffer has 32 storage locations-one for each of the 32 channels supported by the IP330 in the single ended mode of operation. If the IP330 is used in the differential mode of operation each of the 16 channels supported are allocated two Mail Box Buffer locations.

See Table 3.2 which gives the Mail Box Buffer address locations corresponding to each of the 32 channels (or 16 channels in differential mode). In differential mode the first digitized data values will be stored in buffer locations 40H to 5FH while the second digitized values are stored in buffer locations 60H to 7EH. The storage of data in the Mail Box, in differential mode will, continue to alternate between these two Mail Box sections.

The New Data register can be read to determine which Mail Box Buffers contain updated digitized data. A set bit in the New Data register indicates an updated digitized data value resides in its corresponding Mail Box Buffer. In addition, the Missed Data register can be read to determine if a Mail Box Buffer has been overwritten with a new digitized value before the previous one had been read. A set bit in the Missed Data register indicates that a digitized data value has been lost or overwritten.

All register accesses to the IP330 require one wait state with the exception of a read access to the Mail Box Buffer. A read access to the Mail Box Buffer could take up to six wait states if a read is issued while a hardware write of channel data to the same Mail Box is currently underway. Most of the time, contention with hardware writes is not an issue. In which case, one wait state is required for a read access to the Mail Box.

#### MODES OF OPERATION

The IP330 provides five different modes of analog input acquisition to give the user maximum flexibility for each application. These modes of operation include: uniform continuous, uniform single, burst continuous, burst single, and convert on external trigger only. In all modes a single channel or a sequence of channels may be converted. The following sections describe the features of each and how to best use them.

#### **Uniform Continuous-Mode**

In uniform continuous mode of operation, conversions are performed continuously (in sequential order) for all channels between and including the Start and End Channel Values. The interval between conversions is controlled by the interval timer

(Timer Prescaler and Conversion Timer as described in the Conversion Timer Register section). The interval timer must be used in this mode of operation.

After software selection of the uniform continuous mode of operation, conversions are started either by an external trigger, or by setting the software start convert bit. If the external trigger is to be used bit-2 of the Control register must be set low to accept the external trigger as an input signal.

Stopping the execution of uniform continuous conversions is possible by writing 000 to the Scan Mode bits (8-10) of the Control register. See the Control register section for additional information on the Scan Mode control bits and the Control register board address location.

When configured for differential input, the Mail Box functions as a dual level data buffer. The first half of the Mail Box is used to store all selected channel data for the initial pass through the channels defined by the Start and End Value registers. The second half of the Mail Box is then used to store the channel data corresponding to the second pass though all selected channels. Storage of channel data continues to alternate between the first and second halves of the Mail Box Buffer. As seen in Table 3.2, the first half of the Mail Box is defined by word addresses 40H to 5EH while the second half is defined by word addresses 60H to 7EH.

Interrupts can be enabled to activate after conversion of each channel or the group of channels defined by the Start and End Channel Values. If interrupts are configured to go active after the conversion of each channel, the actual interrupt will be issued  $8\mu$  seconds after the programmed interval has lapsed. If interrupt upon completion of a group of channels is selected, an interrupt will be issued  $8\mu$  seconds after the interval time of the last selected channel has expired.

If interrupts are selected to go active after conversion of each channel be sure to program a large enough interval between conversions to allow adequate time for execution of an interrupt service routine. It may also be necessary to allow time for your computer to perform other housekeeping operations between servicing interrupts.

#### **Uniform Single-Mode**

In uniform single mode of operation, conversions are performed once (in sequential order) for all channels between and including the Start and End Channel Values. The interval between conversions is controlled by the interval timer (Timer Prescaler and Conversion Timer as described in the Conversion Timer Register section). The interval timer must be used in this mode of operation.

After software selection of the uniform single mode of operation, conversions are started either by an external trigger, or by setting the software start convert bit. If the external trigger is to be used bit-2 of the Control register must be set low to accept the external trigger as an input signal.

When configured for differential input, the Mail Box functions as a dual level data buffer. However, for Uniform Single Mode, only one pass from the start channel to the end channel is implemented. Thus, only the first half of the Mail Box buffer is utilized. As seen in Table 3.2, the first half of the Mail Box is defined by word addresses 40H to 5EH

Interrupts can be enabled to activate after conversion of each channel or the group of channels as defined by the Start and End Channel Values. If interrupts are configured to go active after the conversion of each channel, the actual interrupt will be issued  $8\mu$  seconds after the programmed interval has lapsed. If interrupt upon completion of a group of channels is selected, an interrupt will be issued  $8\mu$  seconds after the interval time of the last selected channel has expired.

#### **Burst Continuous-Mode**